## A review of advances in pixel detectors for experiments with high rate and radiation

Maurice Garcia-Sciveres<sup>1</sup> and Norbert Wermes<sup>2</sup>

<sup>1</sup>Lawrence Berkeley National Laboratory, Berkeley, U.S.

<sup>2</sup>University of Bonn, Bonn, Germany

#### Abstract

The Large Hadron Collider (LHC) experiments ATLAS and CMS have established hybrid pixel detectors as the instrument of choice for particle tracking and vertexing in high rate and radiation environments, as they operate close to the LHC interaction points. With the High Luminosity-LHC upgrade now in sight, for which the tracking detectors will be completely replaced, new generations of pixel detectors are being devised. They have to address enormous challenges in terms of data throughput and radiation levels, ionizing and non-ionizing, that harm the sensing and readout parts of pixel detectors alike. Advances in microelectronics and microprocessing technologies now enable large scale detector designs with unprecedented performance in measurement precision (space and time), radiation hard sensors and readout chips, hybridization techniques, lightweight supports, and fully monolithic approaches to meet these challenges. This paper reviews the world-wide effort on these developments.

Keywords: semiconductor detectors, tracking detectors, pixel detectors, radiation damage, radiation hard CMOS sensors, hybrid pixels PACS: 29.40.Wk, 29.40.Gx

## Contents

| 1 |            | ectors at the heart of particle physics experiments: challenges and concepts | 9  |

|---|------------|------------------------------------------------------------------------------|----|

| 2 |            |                                                                              | 5  |

|   | 2.1 Dema   | nds and current directions                                                   | -  |

|   | 2.2 Space  | point and direction measurements                                             | 6  |

|   | 2.3 Time   | measurement                                                                  | 11 |

| 3 | Pixel sen  | sors and hybridization 1                                                     | .6 |

|   | 3.1 Plana  | r pixel sensors                                                              | L7 |

|   | 3.2 	 3D-S | sensors                                                                      | 21 |

|   | 3.3 Bond   | ing techniques                                                               | 25 |

$Email\ address:$   ${\tt mgs@lbl.gov}$  ,  ${\tt wermes@uni-bonn.de}$  (Maurice Garcia-Sciveres  $^1$  and Norbert  ${\tt Wermes}^2)$

|   | 3.4                   | Wafer thinning                                               | 27 |

|---|-----------------------|--------------------------------------------------------------|----|

|   | 3.5                   | 3D-integration and through-silicon vias                      |    |

| 4 | 4 Rea                 | dout integrated circuits, data transmission, and power dis-  |    |

|   | $\operatorname{trib}$ | oution                                                       | 33 |

|   | 4.1                   | CMOS ROICs                                                   | 33 |

|   | 4.2                   | Increasing circuit density through 3D integration            | 35 |

|   | 4.3                   | Radiation tolerance of readout integrated circuits           | 36 |

|   | 4.4                   | Total dose radiation damage in CMOS transistors              | 38 |

|   | 4.5                   | Single event upsets and mitigation                           | 42 |

|   | 4.6                   | Analog front end and ADC                                     | 44 |

|   | 4.7                   | Readout architecture                                         | 47 |

|   | 4.8                   | Input hit rates and output data transmission (electrical)    | 51 |

|   | 4.9                   | Optical and wireless transmission                            | 54 |

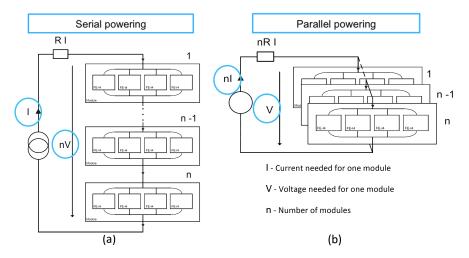

|   | 4.10                  | Power distribution                                           | 55 |

|   |                       | Future development                                           | 56 |

| į | 5 Ad                  | vanced materials: new possibilities for supports and cooling | 58 |

|   | 5.1                   | Cooling                                                      | 58 |

|   | 5.2                   | Supports                                                     | 60 |

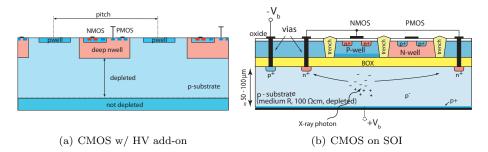

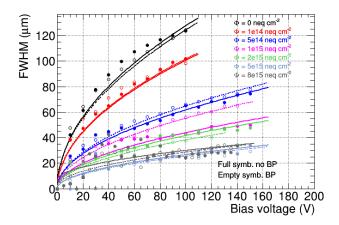

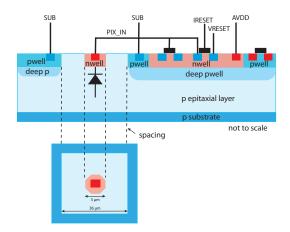

|   | 6 CM                  | OS active sensors: towards monolithic pixels                 | 62 |

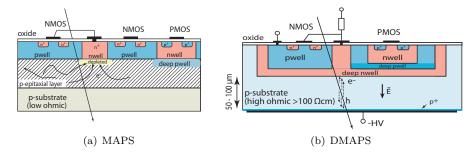

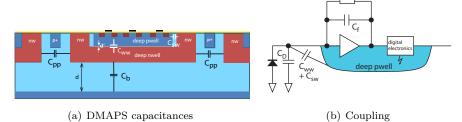

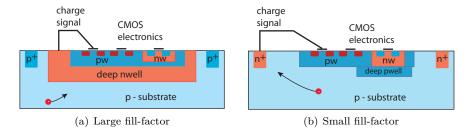

|   | 6.1                   | From MAPS to DMAPS                                           | 62 |

|   | 6.2                   | Designs and technology variants                              | 66 |

|   | 6.3                   | Outlook on DMAPS pixels                                      | 70 |

| , | 7 Sun                 | amary and conclusions                                        | 71 |

# 1. Pixel detectors at the heart of particle physics experiments: demands, challenges and concepts

This article reviews recent advances and future directions in pixel detectors to measure high energy charged particle trajectories in high rate and radiation experiments. A general treatment of pixel detectors can be found in [1]. This review focuses on the on-detector elements, and does not include data acquisition or downstream data processing such as track reconstruction. As there are recent reviews on radiation damage of silicon sensors [2] and on mechanics and cooling of such detectors [3] these topics receive an abbreviated treatment here. The current state of the art is represented by the detectors in operation or under construction at the Large Hadron Collider at CERN, in the ATLAS, CMS, LHC-b, and NA62 experiments.

The ATLAS experiment installed a 3-layer hybrid pixel detector in 2007 [4] and an additional layer at lower radius, inserted within the original detector envelope and therefore called Insertable B-Layer (IBL), in 2014 [5]. The IBL pioneered the use of 3D silicon sensors (in a limited acceptance range) and introduced a new readout integrated circuit (ROIC or readout chip) called FE-I4 [6] with several of the features needed for future high rate detectors.

The CMS experiment installed a 3-layer hybrid pixel detector in 2008 [7], and has replaced it with a new, 4-layer detector in 2017 [8]. The new detector has lower inner radius, significantly lower mass which improves precision, and higher data rate capability needed to cope with increased accelerator luminosity. The upgrade baseline ROIC was redesigned for the outer 3 layers, replacing analog signal readout with on-chip ADCs and digital readout at higher rate [9]. A different ROIC has been designed specifically for the inner layer to handle higher rate and radiation, while keeping to the original footprint. To reduce the mass of the services, radiation hard voltage regulators [10] have been introduced just outside the acceptance, but still inside the CMS inner barrel volume.

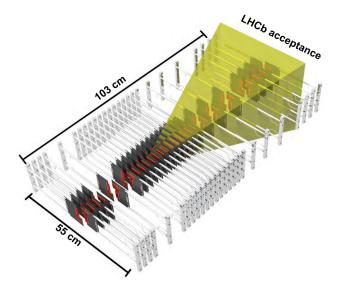

The LHC-b experiment is replacing their strip vertex detector with a 26 plane pixel detector (fixed target geometry) [11]. The detector will use triggerless readout at the full 40 MHz collision rate of the LHC. The high data volume will be handled by up to four 5 Gbps serial outputs per ROIC [12], transmitted over high bandwidth copper cables outside the physics acceptance.

The NA62 experiment has installed a fixed target geometry hybrid pixel detector called Gigatracker to measure timing with high resolution (200 ps) as well as position in each pixel [13]. This is a small area detector, but is pioneering the use of per-pixel timing in particle tracking.

The challenges that drive ongoing development can be broadly categorized into scale, intensity, and performance. Particle physics programs demand pixel detectors with larger outer radius to cope with higher rates, and greater length along the beam direction to increase acceptance. Significant development is therefore focused on how to produce pixel detectors with less effort and lower cost. The two main directions are lower cost production of hybrid pixels and diode sensors (chapter 3), and development of monolithic technology in CMOS foundries (chapter 6).

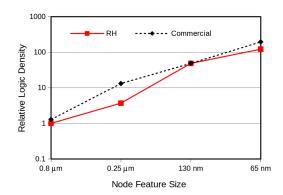

Increasing collider intensity places two main demands on pixel detectors: the ability to store and process greater hit rate per unit area (chapter 4), and higher radiation tolerance (chapters 3, 4, 6). All hits "raining" on a pixel detector unit area must be time-stamped and stored for a trigger latency interval. This means

more memory per unit area in the ROIC, which directly translates to a need for a technology with higher logic density (i.e. smaller feature size, following Moore's Law). Note that the need for higher logic density is not a function of pixel size, but of hit rate per unit area. Smaller pixels are needed to maintain efficiency (to avoid pileup of hits in a single pixel), for resolution (chapter 2), and for radiation tolerance (to keep the leakage current per pixel small). Higher intensity also means that collision events all 'look alike', because every event has a large number of superimposed low energy scatters (pileup), and may or may not have a hard scatter of interest as well, typically with less energy than the sum of the underlying pileup. As distinguishing events of interest becomes more difficult, triggers must increase rate (for a given signal acceptance more background will pass the trigger) and/or use more information, including tracking. Pixel detectors must therefore output much more data (section 4.8).

Achieving larger scale and coping with higher intensity are necessary to increase the physics reach of particle physics experiments. The basic performance of a detector can also improve the physics reach, and therefore, the challenges of scaling and intensity are compounded by the desire to increase performance. Given signal size, sensor capacitance, and device specific transconductance in the ROIC, the pixel front end achievable performance is determined, and actual ROIC's come close to this limit. From a single pixel perspective, the analog performance limit given a power budget and ROIC and sensor technologies is well understood and achieved by the implemented circuits. New developments to increase performance are therefore looking beyond the basic model of a pixel detector as a collection of individual pixels with an output of 3D space points. Correlations between pixels and measurements with internal degrees of freedom (in addition to the usual spatial coordinates) can be used to improve pattern recognition, suppress background, and even provide input to a trigger system. The main degrees of freedom under study are timing, direction, and cluster shape and charge distribution (see chapter 2).

#### 2. Space-time point resolution

#### 2.1. Demands and current directions

The basic detection mechanism of silicon detectors is the generation and drift of mobile charges (e/h) in a depleted silicon junction. This charge cloud has a rich spatial and temporal structure with some dependence on incident particle type and trajectory as well as existing electric and magnetic fields in the silicon. Silicon tracking detectors have typically had granularities in space and time greater than or equal to the charge cloud deposit, resulting in one 3-D space point per particle crossing a sensor with a fairly coarse arrival time stamp, sufficient to associate the point with a given accelerator collision event. Measurement of the magnitude of the collected charge has also been generally available for pixel detectors, and has been used to improve the 3-D space point precision through interpolation as well as for particle identification through specific ionization measurement.

In current detector development we are starting to see increased space and time granularity, in order to measure and make use of the structure of charge deposits. There are many interesting applications of this extra information beyond pure space points. We will give below a few present or anticipated examples: multi-track to cluster association using machine learning, a angular information from cluster length, 3-D cluster shapes using charge arrival time, and disentangling of multiple interactions from sub-nanosecond hit timing.

To be fully exploited, the trend towards fine granularity in space and time, to resolve the charge deposit structure and even the sequence of particle impacts within a detector, must be accompanied by an evolution of the pattern recognition and track fitting algorithms used. Interestingly, algorithm evolution seems to lag detector development. Currently used techniques are still largely based on space points, with extra information added for specific tasks after space point reconstruction. In this chapter we review the basics of space point reconstruction and extend towards new space-time measurement directions as far as they are known and published today. But we expect to soon see modifications of the conventional, well known formulas to include angle, direction, and time measurements.

In general, the tasks of pixel detectors in HEP experiments can be listed as follows:

- 1. Pattern recognition and identification of particle tracks at large background and pile-up levels

- 2. Measurement of primary and secondary vertices;

- 3. Multi-track separation and vertex identification in the core of (boosted) jets:

- 4. Momentum measurement of particles (together with other detectors, like strip detectors);

- 5. Measurement of specific ionization.

Small pixel size keeps the pixel occupancy down at high particle rates (important for item 1) and also leads to good hit resolution. Space point resolutions in the order of  $10\,\mu m$  or less have been routinely achieved at least in one dimension. Achieving the best possible resolution is of utmost importance to cope with the above challenges.

Recent developments (e.g. [14]) also address processing of multi-hit pixel clusters as complex objects to exploit directional information and improve the two track resolution, in particular inside the core of jets.

Time resolutions at the 10–100 ps level have not been realized so far with semiconductor tracking detectors. If achieved this will add another measurement dimension which can be exploited for example to distinguish calorimeter jets coming from a hard interaction from those with large pile-up contributions by using the arrival time distribution (being broad for pile-up jets). Precise timing might also allow coincidence measurements e.g. between tracks in the forward and backward regions of a detector.

#### 2.2. Space point and direction measurements

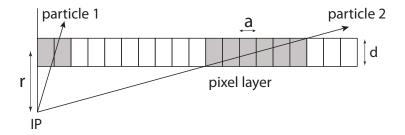

Figure 1 sketches two typical situations for pixel hit clusters. Case (1) represents the case of a particle impinging close to perpendicularly to the pixel module leading to hit clusters of typically one or two pixels. Case (2) represents tracks impinging at steep angles, thus producing larger hit clusters with some directional information when properly treated by reconstruction algorithms, in particular when such clusters appear in several detector layers along a track. Exploiting the hit information this way could become important for hit assignment and track recognition in high track density at the LHC (see for example [14]).

#### Point measurements

The precision of a space-point measurement enters the momentum resolution in a track measurement with N detector layers as given by the Gluckstern formula [15]:

$$\frac{\sigma_{p_T}}{p_T} = \left(\frac{p_T}{0.3|z|} \frac{\sigma_{\text{point}}}{L^2 B} \sqrt{\frac{720}{N+4}}\right) \oplus \left(\frac{\sigma_{p_T}}{p_T}\right)_{\text{MS}} \tag{1}$$

where  $p_T$  is transverse momentum in GeV/c, L is the radial length in m, B magnetic field in T, z is the particle electric charge in elementary units,  $\sigma_{\text{point}}$  is the point resolution of the detectors in m, and N is assumed to be large in this approximation. Important for a precise momentum measurement is the point resolution, but also (quadratically) the total length L of the tracker and the bending field B. The multiple scattering (MS) contribution for a number of detector layers N can be written as

$$\left(\frac{\sigma_{p_T}}{p_T}\right)_{MS} = \frac{0.0136}{0.3 \,\beta \,BL} \sqrt{\frac{(N-1)x/\sin\theta}{X_0}} \sqrt{C_N}, \qquad [L] = m, \ [B] = T$$

(2)

where L is the tracker length projected onto the plane perpendicular to the magnetic field, and  $(x/\sin\theta)/X_0$  is the total material thickness traversed by a particle incident with polar angle  $\theta$  with respect to the beam, in units of the radiation length.  $C_N$  is a factor depending on the number of layers:  $C_N = 2.5$  for the minimum of three layers to measure a circle; it approaches  $C_N = 1.33$  for  $N \to \infty$  (continuous scattering).

Even though the hard collisions at the LHC produce high energy jets, low momentum tracks around and below 1 GeV/c transverse momentum play an

important role, especially in the forward direction. For example, efficient jet tagging - jets in general and b-jets in particular - and suppression of pile-up contributions by primary vertex identification suffer from imprecise detection of low momentum particles. For the HL-LHC, low  $p_T$  tracks will become even more important as pile-up increases. This renders low mass (low  $x/X_0$ ) extremely important.

Similarly, the precision of secondary vertex measurement with an N layer tracker can be expressed by the impact parameter resolution (here in linear extrapolation):

$$\sigma_{d_0} \approx \frac{\sigma_{\text{point}}}{\sqrt{N}} \sqrt{1 + \frac{12(N-1)}{(N+1)} \left(\frac{r}{L}\right)^2} \oplus \theta_0 \, r_{pv} \sqrt{\frac{N(2N-1)}{6(N-1)^2}}$$

(3)

where the first term results from the extrapolation from the tracker to the primary vertex with r/L being the ratio of the extrapolation distance to the tracker length. The point resolution enters linearly. For a pixel detector with four layers as in ATLAS, at radii between 3.3 cm and 12.3 cm and with a point resolution of about 10  $\mu$ m, this yields  $\sigma_{d_0} \approx 12.5 \,\mu$ m without multiple scattering.

The second term is due to multiple scattering approximated by assuming extrapolation from the first layer to the primary vertex, the slope of which is smeared by multiple scattering, with  $\theta_0$  being the multiple scattering angle [16]:

$$\theta_0 \approx \frac{0.0136 \,\text{GeV/c}}{\beta p} \sqrt{x/X_0} \,,$$

(4)

and  $r_{pv}$  the distance of the first pixel layer to the primary interaction vertex. For a 4-layer geometry like in ATLAS and a material thickness of typically around  $3\% X_0$  the multiple scattering contribution to the  $d_0$  resolution yields

$$\sigma_{d_0}^{\rm scat} \approx \frac{90 \,\mu{\rm m}\,{\rm GeV/c}}{p} \,.$$

(5)

Spatial resolution also impacts pattern recognition performance in complex interplay with pixel occupancy, material thickness, and layout. However, pattern recognition algorithms are outside the scope of this review.

Space-point reconstruction methods

In designing a pixel detector one selects the (initial) amount of charge sharing. The tuning parameter for a given planar sensor thickness is the ratio of the Lorentz angle (the deviation from perpendicular to the sensor surface of the drift path of charges in a magnetic field [17]), to the tilt angle of the module with respect to perpendicular particle passage. While charge sharing between pixels allows for better spatial resolution by charge interpolation, a signal decrease caused by irradiation during the detector's lifetime demands minimal charge sharing. Whether collected charge causes a hit also depends on the pixel threshold. Noise deteriorates the precision of reconstruction and causes spurious hits.

For the present LHC pixel detectors with relatively large pixels, covering mainly central rapidity and not having too steep incidence angles, the number of hits in a cluster from a single track is rarely greater than 2. At large incidence angles in the forward regions of a barrel pixel detector or in the future with

Figure 1: Pixel hit clusters for tracks under different incident angles.

smaller pixel sizes, the cluster distribution can become much larger and this information can also be exploited (see below).

Resolutions achievable with classical space point reconstruction methods can be classified as follows:

- For single hit clusters independent of having binary (yes/no) or analog origin resolution is given by the well-known pitch/ $\sqrt{12}$  RMS resolution assuming a flat prior distribution of track position within the pixel (most conservative assumption). For an arbitrary given cluster size and track direction the resolution still is constant and is determined by the RMS of the prior track distribution that can produce a cluster of this size. For large clusters, high spatial resolution is possible even with binary readout, due to the averaging of many pixels.

- Analog hit information can be obtained at the expense of a larger total data volume (see e.g. [4][18] for ATLAS) or by processing the analog pulse off the module as is done in CMS [7]. In this case the reconstructed hit position  $x_{rec}$  can be obtained e.g. by the centre of gravity method

$$x_{rec} = \frac{\sum (S_i + n_i) x_i}{\sum (S_i + n_i)} \tag{6}$$

where the  $S_i$  and  $n_i$  are the signal and noise fractional weights, respectively, and  $x_i$  is the center of each individual pixel in the cluster. The achievable resolution is:

$$\sigma_x^2 = \sigma_n^2 \left[ \left( \sum_{i=1}^N x_i^2 \right) + N \langle x^2 \rangle \right] + \mathcal{O}(\sigma_n^3),$$

(7)

where  $\sigma_n$  denotes uncorrelated noise and N is the number of hit pixels [19, 20].

• If two hit clusters is the most common case for pixel detectors the  $\eta$ reconstruction method [21, 22] is optimal for space reconstruction of Gaussian charge clouds, since detector effects are automatically included. For

two adjacent left and right electrodes the function

$$\eta = \frac{S_L}{S_L + S_R} \,, \tag{8}$$

| Experiment | R/O method | pitch [µm] | inc. angle | $\sigma_x$ [µm] |

|------------|------------|------------|------------|-----------------|

| ATLAS [23] | binary/ToT | 250        | 0°         | 66.5            |

| ATLAS [23] | ТоТ        | 50         | 0°         | 10              |

| ATLAS [4]  | ТоТ        | 50         | 10°        | 7               |

| CMS [24]   | analog     | 150        | 0°         | 44              |

| CMS [24]   | analog     | 150        | 30°        | 21              |

| CMS [24]   | analog     | 100        | 0°         | 9.4             |

Table 1: Spatial resolutions obtained with the ATLAS and CMS pixel detectors under LHC conditions. R/O stands for Readout and ToT for Time over Threshold.

constructed from measured signals  $S_{L,R}$  is position dependent,  $\eta = \eta(x)$ , and the hit position is obtained from the inverse  $\eta^{-1}$ :

$$x_{rec} = \eta^{-1} \left( \frac{S_L}{S_L + S_R} \right) = \frac{a}{N} \int_0^{\eta} \frac{dN}{d\eta'} d\eta' \,. \tag{9}$$

where  $dN/d\eta'$  is the probability distribution (with normalization N) of hits vs  $\eta'$  resulting from uniform illumination (random x distribution), and a is the channel pitch. Including noise  $n_{L,R}$  (fractional, i.e. in units of the signal) (9) becomes [19][20]:

$$x_{rec} = \eta^{-1} \left( \frac{S_L + n_L}{S_L + S_R + n_L + n_R} \right) = \eta^{-1} \left( \frac{\eta(x) + n_L}{1 + n_L + n_R} \right)$$

$$\approx x + \frac{d\eta^{-1}(s)}{ds} \Big|_{\eta(x)} \cdot \left( n_L (1 - \eta(x)) - n_R \eta(x) \right)$$

(10)

with  $s = \eta(x) + n_L(1 - \eta(x)) - n_R\eta(x)$ . Obviously, a steep response function  $\eta$  yields the best resolution, given by:

$$\sigma_x^2 = \sigma_n^2 \left\langle \frac{1 - 2\eta + 2\eta^2}{\eta'^2} \right\rangle + 2\langle n_L n_R \rangle \cdot \left\langle \frac{\eta^2 - \eta}{\eta'^2} \right\rangle, \tag{11}$$

where the second term vanishes for uncorrelated noise,  $\langle n_L n_R \rangle = 0$ .

By using analog information either directly (CMS) or via a Time over Threshold (ToT) digitization (ATLAS), resolutions as shown in table 1 have been obtained (references in table). The ToT method is explained in section 4.6.

Limitations to the space point resolution of a pixel detector

When aiming for ultimate spatial resolutions with hybrid pixel detectors the following limitations are encountered:

- Since for hybrid pixels the chip's pixel area must match the sensor's pixel area the smallest pixel size is determined by the amount of CMOS electronics needed to amplify, discriminate, and process the hit information in the area occupied by the pixel cell. Third generation chips for high hit rate achieve about  $50\times50~\mu\text{m}^2$  or  $25\times100~\mu\text{m}^2$ , limited by logic density as explained in section 4.

- The signal of a traversing MIP (Minimum Ionizing Particle) spreads due to diffusion according to  $\sigma_x = \sqrt{2Dx/v_D}$ , where D is the diffusion constant,

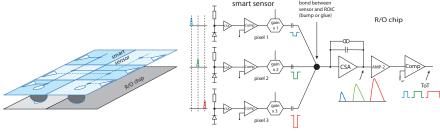

(a) Coupling of smart sensor and readout chip

(b) Function principle

Figure 2: In-pixel en- and decoding using a 'smart sensor' bonded to a pixel readout chip (here showing 6 smaller sensor pixels bonded to two readout pixels). The sensor pixels contain amplifications with adjustable gains (here  $\times 1, \times 2, \times 3$ ). The gains are set such that the origin of a hit can be decoded from the output pulse height encoded as ToT.

x the drift distance to the electrode and  $v_D$  the drift velocity. For a typical detector thickness of 150–200 µm,  $\sigma_x$  becomes 4–8 µm. Hence pixel pitches well below this (at the same sensor thickness) would lead to excessive charge sharing.

• Pixel hybridization technology (see section 3) can currently cope with bump pitches in the order of  $25-50\,\mu\text{m}$ . The technological limit for galvanic or evaporation methods for the coming decade seems to lie in the order of  $5-10\,\mu\text{m}$  [25] (see also section 3.3).

#### In-pixel decoding

It has been proposed [26] to effectively achieve smaller pixel size by encoding and decoding the pixel sensor cell by means of 'smart sensors' when using depletable substrates with a CMOS electronics layer (see also section 6).

Figure 2 shows the principle. Two pixels of the readout chip (e.g. FE-I4 with  $50\,\mu\mathrm{m} \times 250\,\mu\mathrm{m}$  each) match six (sub-)pixels of the smart sensor with sizes  $33\,\mu\mathrm{m} \times 125\,\mu\mathrm{m}$ . Three sub-pixels at a time are connected to one of the two FE-I4 inputs via AC coupling, either by a capacitor included in the sensor pixel plus DC connection (bump bonding) to the corresponding FE-I4 chip pixel, or by gluing the sensor chip/wafer to the FE-I4 wafer, in which case the coupling is also capacitive. The digital (voltage) output pulse of the smart sensor is capacitively coupled into the CSA input of the readout chip. The three digital output stages of the sensor pixels can be programmed with three different gains (high, medium, low) such that digital pulses of different height are capacitively coupled to the input of FE-I4 depending on which of the sub-pixels has been hit. Further processing of the pulse by the FE-I4 amplification and discrimination stages turns different pulse heights at its input into different ToT values at the output. Hence the sub-pixel hit by the MIP is finally decoded from its ToT value. Test beam measurements demonstrated the functionality of the method [27, 28].

#### Directional information from hit clusters

Multivariate algorithms like artificial neural nets (ANN) have now also entered the area of hit/cluster to track association for improved track reconstruction in high multiplicity environments. The single hit precision is not the only

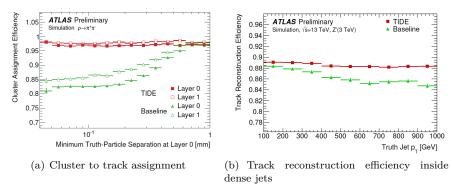

Figure 3: Improvement in hit cluster assignment and tracking efficiency using artificial neural networks to resolve merged clusters for Tracking In Dense Environments (TIDE), taken from [14]. (a) Cluster assignment efficiency as a function of separation of two pion tracks from simulated  $\rho^0 \to \pi^+\pi^-$  decays at the innermost pixel detector layers. (b) Track reconstruction efficiency inside dense jets for high  $p_T$  jets.

figure of merit to tune. One must also optimize the capability of cluster shape analysis (especially for inclined tracks) and the analysis of pattern information of clusters from dense tracks over several layers. For example in [14] it is shown how successive employment of ANNs can improve (a) the association of merged clusters to tracks, (b) track reconstruction inside the core of (boosted) jets, and (c) heavy flavour and  $\tau$ -jet identification. The amount of charge per pixel, for instance provided by the ToT technique [4], and a precise knowledge of the pixel coordinates is already sufficient as input for the ANN to identify merged clusters efficiently. The emission of  $\delta$ -rays and secondary interactions of tracks prevent a perfect ANN performance. The approach benefits from knowing the incident angle of tracks, estimated from the coordinates of modules with respect to the beam spot, and from correlating information from consecutive layers of the pixel detector [14]. Figure 3(a) demonstrates using simulation the gain in cluster assignment efficiency using this technique on a sample of simulated  $\rho^0 \to \pi^+\pi^$ decays. Figure 3(b) shows the improvement in tracking efficiency inside dense jet-cores obtained using the ANN-based improved merger identification. Improvement in high- $p_T$  heavy flavour identification of 7–13% (b-tagging and b-jet identification) and of 5% in 3-prong  $\tau$ -jets above  $p_T = 600 \,\text{GeV}$  is the result [14].

## 2.3. Time measurement

The charge collection time, i.e. the time until the arrival of the last electron at the pixel electrode, typically is in the order of 3–10 ns, depending on sensor thickness and E-field. The induced current pulse at the electrode instantly starts with the particle passage and consists of the incoherent sum of induced pulses from each carrier's path towards (e<sup>-</sup>) and away (h<sup>+</sup>) from the pixel electrodes. The individual contributions are weighted by the pixel weighting field (see e.g. [29, 1, 19]) leading to the fact that the carriers' paths close to the pixel implant have the strongest contributions to the signal. In a typical pixel detector the current pulses are integrated by the input stage of the subsequent readout chip, a charge sensitive amplifier (CSA). While such a readout method has low noise

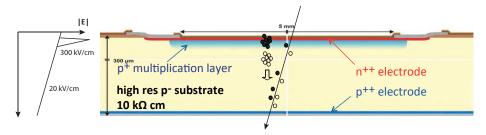

Figure 4: Cross section through an LGAD structure using a high ohmic p-type bulk and featuring a metallurgical junction underneath the  $n^{++}$  electrode acting as the amplification layer (adapted from [38]). The shape of the electric field strength is indicated on the left.

performance<sup>1</sup> it does not allow timing measurements at or below 100 ps, values at which timing becomes interesting for high energy particle detection.

For a time coordinate measurement to reach equivalent spatial resolutions in the cm to mm regime, time resolutions of the order of a few tens of picoseconds are needed. To achieve this with pixel detectors, where charge collection times are in the ns range, is a real challenge. Recently, amplification structures in silicon have been brought forward to cope with these demands [31, 32, 33]. Potential benefits are the suppression of pile-up jets by recognizing the time-wise association of tracks to a primary vertex.

#### LGAD structures

In order to reach into the picosecond timing regime with silicon detectors, in-silicon amplification can be employed. Avalanche generating silicon based devices have been developed in the context of photodetectors (see for example [34],[35],[36]). They can be distinguished by their operation mode, either as linear avalanche photodiodes (APD) operating in a linear amplification mode or as so-called Geiger APDs operating near the breakdown point thus sensing a light pulse by a large breakdown pulse with follow-up recovery time. Timing in Geiger-mode operation will be governed by the time jitter introduced by the breakdown process (multiplication jitter), similar to the case for gaseous detectors where fast timing is addressed for example with RPCs (resistive plate chambers) [37]. Another approach has been chosen by [31], namely by operating avalanche silicon diodes at a low gain operation point, so-called Low Gain Avalanche Diodes, LGADs.

In order to create precise time stamps, fast and large signals and low noise are needed. The *slew rate* can serve as a figure of merit, defined as

$$\frac{dV}{dt} \approx \frac{\text{signal height}}{t_{rise}} \,. \tag{12}$$

Figure 4 shows a principal cross section of an LGAD structure [38]. In a  $p^-$  bulk, faced on both surfaces by the usual very highly doped<sup>2</sup>  $n^{++}$  and  $p^{++}$  electrodes rendering the structure of the detector, an additional, highly doped  $p^+$  layer  $(N_A \approx \mathcal{O}(10^{16}/\text{cm}^3))$  is implanted immediately underneath the  $n^{++}$

$<sup>^{1}</sup>$ Typical noise values are on the order of  $150\,\mathrm{e^{-}}$  for the present LHC detectors [4, 7] and will be around  $80\,\mathrm{e^{-}}$  for future detectors with smaller pixels [30].

<sup>&</sup>lt;sup>2</sup>We here adopt the notation p<sup>++</sup> for  $N_A \gg 10^{16}/\text{cm}^3$ , likewise for  $n^{++}$ .

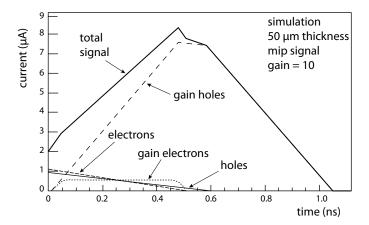

Figure 5: LGAD signal pulse detailing the contributions from electrons and holes before and after amplification following weighting field simulations [39]. The contributions from both electron and hole signals are shown before and after amplification as well as the total signal (adapted from [38]).

electrode, thus creating a very local high electric field of up to  $300 \,\mathrm{kV/cm}$ . This is the multiplication layer amplifying all arriving electrons by a factor of the order of 10-20, thereby creating secondary e/h-pairs.

The signal induced on the electrodes therefore has several components (see fig. 5):

- Electrons and holes drifting from the point of creation along the track towards their respective collection electrodes. The individual e/h parts of this contribution are small before amplification takes place and end when the last carriers have arrived at their respective electrodes.

- Amplification electrons created in the multiplication layer reach the top electrode (fig. 4) almost instantaneously and their contribution to the induced signal current  $i_S(t)$  is close to negligible, because according to the Shockley-Ramo theorem [40, 41] -

$$i_S(t) = e\vec{v}_D(t) \cdot \vec{E}_w$$

with  $E_w$  = weighting field and  $v_D$  = drift velocity, there is almost no current contribution since the drift duration for electrons is quasi non-existent and ending before the next primary electrons reach the amplification layer.

By contrast, the multiplied holes drifting from the amplification layer towards the backside contribute to i<sub>S</sub>(t) as long as they are drifting. Their contribution adds up, provided that the weighting field is formed such that it does not suppress contributions from distant holes too much. This implies that the pixel/pad implant widths must be large compared to the implant distances and should be in the same order of magnitude as the detector thickness.

As can be seen from fig. 5, a large slew rate and hence fast timing requires fast (primary) electron arrival at the amplification zone together with fast (ampli-

fied) hole movement away. Short bunching and fast movement in high fields ( $\sim 20\,\mathrm{kV/cm})$  benefit from thin sensors.

The time resolution has several contributions [42]:

$$\sigma_t^2 = \underbrace{\left(\frac{V_{th}}{dV/dt}\Big|_{rms}\right)^2}_{\sigma_{\text{time walk}}^2} + \underbrace{\left(\frac{\text{Noise}}{dV/dt}\right)^2}_{\sigma_{\text{noise}}^2} + \sigma_{\text{arrival}}^2 + \sigma_{\text{dist}}^2 + \sigma_{\text{TDC}}^2$$

(13)

The first term represents time walk introduced by different signal pulse heights due to different energy deposits coming from Landau fluctuations in the energy loss process and its resulting pulse height fluctuations at the discriminator input. Minimization of this term is possible e.g. by employing a constant fraction discrimination or a ToT correction architecture in the readout. The second term is noise jitter, i.e. time fluctuations due to noisy signals. Both contributions are made small when large slew rates are achieved. An irreducible contribution comes from fluctuations resulting from non-uniform depositions of charge along the particle track moving towards the amplification junction, hence causing an intrinsic jitter in the arrival time  $\sigma_{arrival}$  (third term). Fluctuations from secondary ionizations and from the amplification process enter here as well. The thinner the detector the less disturbing is this effect. An additional  $4^{th}$  contribution is signal distortion due to non-uniform weighting field regions and variations in (non-saturated) drift velocities. The final term is time fluctuations due to uncertainties in the time digitization. It is assumed that the latter can be made negligible (below 10 ps) with GHz TDCs.

The key ingredients for fast timing and small time jitter are thin detector substrates  $(\mathcal{O}(50\,\mu m))$  providing three essential benefits:

- larger slew rate ( $\times 1.6$  slew rate increase going from  $d = 100 \,\mu m$  to  $50 \,\mu m$  at a gain of 20),

- better bulk radiation hardness,

- smaller arrival time fluctuations due to a shorter charge deposition path.

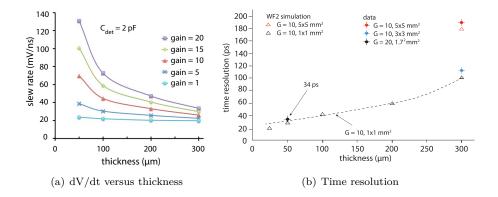

In fig. 6(a) the slew rate is plotted against the diode thickness for different gains assuming an input capacitance of  $2 \,\mathrm{pF}$  [38]. It is evident that large slew rates can be obtained with thin detectors and sufficient gain ( $\gtrsim 10$ ). Much higher gains compromise the S/N ratio, because bulk shot noise is also amplified by the amplification structure (called excess noise) such that there is an optimal gain for maximum signal-to-noise (see for instance [36] or [42]).

Prototype LGAD structures have been fabricated [38, 43] with relatively large pads (from  $8\times8\,\mathrm{mm^2}$  to  $1\times1\,\mathrm{mm^2}$ ), rather than pixels, mainly to validate the underlying models and simulations of the achievable time resolution. Figure 6(b) shows the predicted time resolution by simulations [39] as a function of the detector thickness. At the right hand side measured data from 300  $\mu\mathrm{m}$  thick LGAD pad detectors are compared with simulations. Extrapolation to thin detectors yields time resolutions in the order of 30 ps. Very thin detectors have only recently become available. In a test beam measurement with 180 GeV pions, a 50  $\mu\mathrm{m}$  LGAD sensor with  $1.2\times1.2\,\mathrm{mm^2}$  pads has been characterized, achieving 34 ps time resolution at a bias voltage of 200 V [44], in excellent agreement with predictions from weighting field simulations (fig. 6(b)).

Figure 6: LGAD weighting field simulations and measurements: (a) slew rate as a function of detector thickness for different amplification gains (simulation); (b) comparison of time resolutions from weighting field simulations (WF2) and from test beam measurements using constant fraction discrimination. Open triangles are simulation points, crossed circles are measured resolutions without errors given (bars do not indicate the measurement errors). Note the different pad sizes entering the figure. The WF2 simulations for  $1x1\mu m^2$  are underlined by the dashed line only to guide the eye. The data are taken from [38],[43],[44],[33], and [42].

A major concern for the use of LGADs at the HL-LHC is their performance in high radiation areas. Apart from the usual effects caused by radiation in silicon detectors like leakage current increase and deteriorated charge collection efficiency, effective doping changes play a sensitive role. Since the metallurgical junction providing the amplification gain requires p-doping concentrations of order of  $10^{16} {\rm cm}^{-3}$ , radiation induced acceptor removal will have detrimental effects upon the gain. Detailed radiation studies are currently ongoing [42], including very thin sensors ( $\lesssim 50\,\mu{\rm m}$ ) and devices with gallium substituted as p-dopant in the amplification implant instead of boron, to reduce interstitial capture that scales with atomic mass [45]. Another proposed method is to use carbon-enriched wafers with (abundant) carbon being trapped by silicon interstitials rather than boron.

Currently LGADs are not yet discussed for pixel tracking detectors but rather as precision timing layers, aiming to distinguish primary vertex positions (in z) from each other (see e.g. [46]). CMS-TOTEM is planning to use LGADs in Roman Pot stations [47].

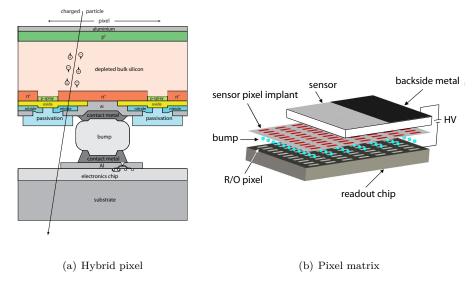

Figure 7: Hybrid pixel detector: (a) Layout of an individual pixel cell having a sensor and an electronics cell in 1–1 correspondence; (b) a hybrid pixel matrix; sensor and electronics chip have pixels of the same size, bonded to each other by means of bump contacts.

#### 3. Pixel sensors and hybridization

'Hybrid pixels' including a sensor (electronically passive) and a readout chip as separate entities (fig. 7) currently are the state-of-the-art technology for large scale pixel detectors in most particle physics experiments [1]. For both parts, the radiation requirements at LHC-type experiments constitute a challenge which is addressed by dedicated R&D and process engineering techniques. In this chapter we describe passive sensor types used in hybrid pixel assemblies, to be contrasted to CMOS active monolithic sensors that integrate electronics circuitry and sensor, described in chapter 6. The mechanical and electrical mating of sensor and readout chip, called hybridization, requires state-of-the-art processing technologies, also described in this chapter (section 3.3). The hybridization mating partner, the readout chip is described in detail in chapter 4.

After the success of planar sensors (section 3.1) in LHC run-1, having planar pixel implants at one side of the sensor and being fabricated using 4" sensor wafer technologies, the desire for large detector modules at affordable cost has fueled the move to 6" and possibly even 8" wafer sensor technologies. In line with this a better understanding of radiation damage effects and radiation hard sensor device engineering became a research branch on its own, coordinated within the CERN RD50 collaboration [45].

Radiation hard device engineering includes using silicon with increased oxygen content supplied in the growth process [48, 49, 50] and operation at low-temperature, both employed to reduce the damage's impact on the detector performance. Furthermore, so-called 3D-silicon sensors [51] (see section 3.2) have been developed having vertically structured electrodes fabricated within the volume of the silicon substrate (fig. 11). Their main feature is a better ratio of ionization thickness to charge collection distance than for planar sensors. After an operation performance demonstration in the first pixel upgrade of ATLAS

(Insertable B-Layer, IBL [5]), an innermost pixel barrel layer at a distance of  $3.5\,\mathrm{cm}$  from the interaction point, equipped with 25% 3D-Si sensors (at high  $\eta$ ) and 75% planar pixel sensors, both sensor types now compete for the HL-LHC upgrade as pixel sensors for the radiation hot areas near the interaction point.

A challenge for both sensor types imposed by the radiation fluences of  $>10^{16} \, \mathrm{neq/cm^2}$  is the small foreseen sensor thickness (100–150  $\mu \mathrm{m}$ ) and the correspondingly increased handling and hybridization difficulty.

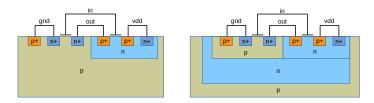

Another advance in cost reduction of sensor wafers has been made possible by the availability high quality p-substrate material ( $\gtrsim 2\,\mathrm{k}\Omega\mathrm{cm}$ ). With n-in-p type sensors cost-efficient single sided processing suffices for fabrication while maintaining electron collection (n-type pixels). During the initial LHC pixel development period (late 1990s) high ohmic p-type sensor wafers were not favoured, largely for reasons of historical development<sup>3</sup>, and  $n^+$ -in-n planar pixel sensors have been used instead, requiring processing steps on both sides of the wafer.

With CMOS technology vendors becoming more open to smaller market customers, the use of high ohmic 8" wafers fabricated in (much lower cost) CMOS processing lines become options for (planar) sensor options (see section 3.1).

Currently, therefore, the trend in hybrid pixel module development goes to large readout chips and thin sensors, preferentially using p-type bulk material, all being beneficial for cost, radiation tolerance, and detector mass, while the handling and hybridization demands increase. The latter together with the increased interest for large area coverage using pixel detectors also revived collaboration with industry to develop lower cost hybridization techniques with thinner wafers/chips.

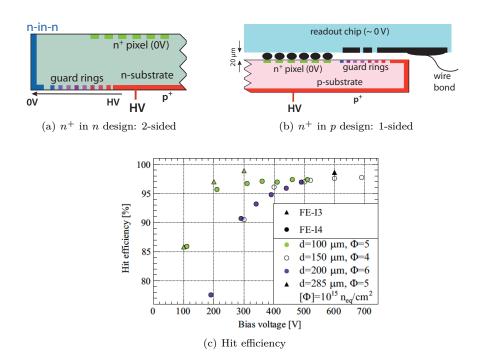

### 3.1. Planar pixel sensors

The proven standard of planar pixel sensors at the LHC experiments has  $n^+$  pixel implants on n-type substrate material as shown in fig. 8(a). The fabrication demands double-sided processing. The negative bias potential on the backside is brought down to zero potential at the sensor edge by a many guard ring structure implanted on the backside. The pn-diode is initially on the unstructured backside of the sensor, changing to the electrode side after radiation has turned the bulk's  $n^-$  doping into effectively p-type (type inversion). For typical substrate resistivities of  $2-5\,\mathrm{k}\Omega\mathrm{cm}$ , this happens after fluences of some  $10^{12}\,\mathrm{neq/cm^2}$ . After type inversion the depletion zone grows from the electrode side into the bulk guaranteeing that signals induced by moving charges can be sensed on the pixels even if the substrate is no longer fully depleted, i.e. not depleted at the side opposite to the pixels. To prevent an electron accumulation layer from short circuiting the  $n^+$ -in-n pixels before type inversion, shallow p-doping is used in between the pixel electrodes, with a smoothly changing doping profile preventing high field corners. Details are given in [1].

With increasing radiation fluence the bias voltage needed for sufficient depletion must be increased, eventually reaching values of more than  $500\,\mathrm{V}$  at

$<sup>^3</sup>$ Single sided Si sensor development had begun using n-substrate material with hole collection on p-electrodes. For radiation tolerance reasons electron collection became favored leading to  $n^+$ -in-n structures with double sided processing. For n-in-p sensors it then has taken time to develop n-side multi-guard-ring structures and reliable HV bias isolation from the electronics before high quality p-type sensors were fabricated.

Figure 8: Planar sensors: (a) LHC conventional  $n^+$ -in-n design requiring 2-sided wafer processing; (b)  $n^+$ -in-p design with single-sided processing (bump) bonded to a readout chip. Note the small distance between readout chip and guard ring implants; (c)  $n^+$ -in-p sensor hit efficiency as a function of bias voltage for different fluences and various thicknesses [52].

fluences around and beyond  $10^{15}$  neq/cm<sup>2</sup>. For the innermost layers close to the interaction point this corresponds to detector lifetimes of only a few years at current LHC luminosity.

The development of planar sensors for the LHC high luminosity upgrade has therefore concentrated on tailored designs guaranteeing high fields and sufficiently large depletion depths after fluences of up to and above  $10^{16}$  neq/cm<sup>2</sup>. This has been achieved using n<sup>+</sup> pixel implants in p-substrate material and thin (100-150  $\mu$ m) sensors operated at bias voltages of 500-700 V [52]. While providing smaller signals per MIP, the benefits of thin sensors are higher electric fields as well as shorter and faster electron collection for a given bias voltage and hence better radiation tolerance. Thin 6" or even 8" sensor wafer production is enabled by techniques employing SOI or Si-Si handling wafers, or by thinning (e.g. by cavity etching) and forming a back side ohmic contact at low temperature after the front side processing is complete. Currently the limit in thickness is considered to be around 50  $\mu$ m [53].

The guard ring designs, bringing down the potential from the bias implants (HV) to the pixel implants (0V), play an important role in optimizing the breakdown behaviour of sensors after irradiation. The number of rings, implant distance and size, as well as metal overhangs for vertical field suppression are the parameters to optimize. Optimal performance regarding radiation tolerance has been obtained [53] with 10–11 rings with metal overhangs on both sides of the implant over a total length of 350  $\mu$ m. The distance from the edge to the active part of the sensor is  $\gtrsim 400 \,\mu$ m. Other designs trying to minimize this distance

make use of etched and doped edges, called active edges, reaching values down to about 50  $\mu$ m [54].

Figure 8(a) shows a planar pixel design as used in present LHC hybrid pixel detectors (200 µm thick,  $n^+$ -in-n design) compared to a thin  $n^+$ -in-p design (fig. 8(b)). Note that, if cost saving single sided processing is to be used, the guard ring structure needs to be placed on the electrode side and is thus in very close proximity ( $\lesssim 20 \,\mu\text{m}$ ) to the readout chip, a challenge for the design. Dedicated passivation with BCB (benzocyclobuthene) or parylene, however, appears to be able to solve this issue [55]. Figure 8(c) shows that high hit efficiencies can be achieved after irradiation with thin sensors for bias voltages in excess of 500 V.

## Use of 8" wafers and CMOS foundries

It is also possible to fabricate planar sensors on 8" wafers using high ohmic substrates either in dedicated sensor fabrication facilities or by employing CMOS foundries, as has been successfully demonstrated for strip and pixel sensors [56, 57]. This has the following advantages compared to the standard small volume sensor fabrication:

- Large volume production lines can be used with price advantages, suited in particular for large area detectors, e.g. in outer tracking layers at collider experiments.

- Wafer sizes of 8" or 12" are a commercial standard allowing large sensors when stitching over reticle boundaries is applied. Stitching is a method to cross the boundaries between reticles of a wafer with metal lines and implant areas, widely applied in the digital imaging industry [58]. Current reticle sizes are about 25×25 mm². By putting individual building blocks of a design separately (rather than together) on the reticle/mask one can join them together over the reticle's boundary by special lithographic programming, thus allowing IC fabrication of sensor sizes much larger than the reticle area of the CMOS process.

- The wafers can be purchased with solder bumps already provided by the CMOS vendor (e.g. so-called C4 bumps [59], pitch  $\gtrsim 150 \,\mu\text{m}$ ).

- One or two metal layers can be exploited for AC coupling of the sensor cell to the amplifier and for connection redistribution, e.g. to connect amplifier inputs to pixels in areas not covered 1:1 by readout chip cells (regions in between readout chips).

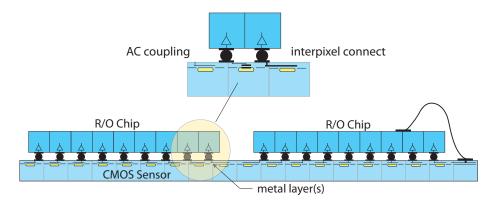

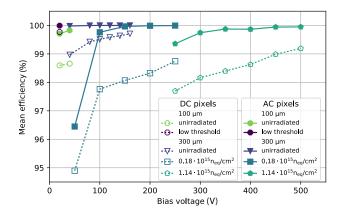

A sketch illustrating some features employing passive CMOS sensors is shown in fig. 9. Measurements on passive CMOS pixel sensors,  $100\,\mu\mathrm{m}$  and  $300\,\mu\mathrm{m}$  thick, irradiated to fluences of  $1.1\times10^{15}\,\mathrm{neq/cm^2}$  have shown lab and test beam performance equal to those of planar sensors fabricated in dedicated sensor production lines [60]. Figure 10 shows the mean hit efficiency as a function of bias voltage measured with 3.2 GeV electrons for DC and AC coupled passive CMOS sensors bonded to the ATLAS readout chip FE-I4. In particular the AC-coupled devices show excellent performance without any efficiency losses. The DC devices are a bit less efficient due to the area taken by the punch-through dot for biasing of the pixel implants.

Figure 9: Hybrid pixel module using passive CMOS pixel sensors (schematic). Depleted sensor employing CMOS technology with 1-2 metal planes that can be used for (i) AC coupling and (ii) rerouting. The insert details these features. The yellow area in every pixel denotes the charge collection node.

Figure 10: Hit efficiency measured in 3.2 GeV electron test beams [60] of passive CMOS pixel sensors as a function of bias voltage, unirradiated and for two fluence levels. For low threshold, unirradiated, there is only one point for each thickness at minimal bias voltage.

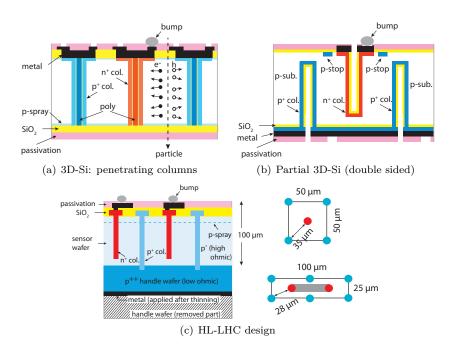

Figure 11: 3D-Si sensors: (a) Design (single sided) with columns going completely through the sensor bulk [62]; (b) double sided design with columns entering from both sides, but not reaching through (adapted from [66]); (c) thin design optimized for HL-LHC (adapted from [67]) with two top view sketches for  $50 \times 50 \,\mu\text{m}^2$  and  $25 \times 100 \,\mu\text{m}^2$  pixel sizes, respectively.

## 3.2. 3D-Si sensors

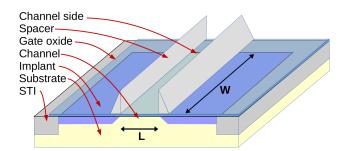

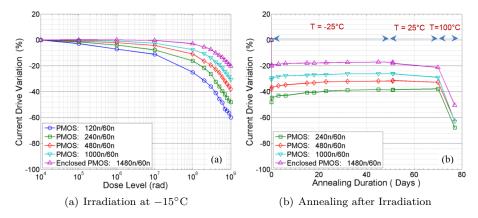

So-called 3D-silicon sensors have been developed since the late 1990s [51, 61] featuring columnar electrode implants driven into the Si substrate perpendicular to the sensor surface (fig. 11). The electrode distance is made smaller (50 $\mu$ m) than the typical sensor thickness (200-250 $\mu$ m), thus rendering a shorter average drift distance for particles impinging on the sensor face than in the case of planar sensors (compare fig. 7(a) to fig. 11(a)). In addition, high drift fields are obtained with still moderate bias voltages. Both these facts result in an increased radiation tolerance due to a reduced trapping probability.

The 3D-Si technique has been developed over many years. The first structures were fabricated at Stanford (later also at Oslo) [62] using single sided processing with columns reaching completely through the bulk (called 'full-3D'and shown in fig. 11(a)). Further development by CNM [63] and FBK [64] of sensors used in the ATLAS IBL detector, resulted in double-sided 3D designs with columns entering the bulk from both sides, either in full-3D or in partial-3D (shown in fig. 11(b)). The process fabricates about 10  $\mu$ m diameter columns by etching, followed by a 1  $\mu$ m polysilicon layer covering the inside of the etched holes, then passivated by a wet oxide [63]. In addition the sensor edges can be fabricated with active edge implants thus rendering sensors with an unrivaled active area fraction [65]. More details on etching holes into silicon can be found in section 3.5.

Within the ATLAS IBL detector 3D-Si pixel sensors have been proven to operate well in a running experiment [5]. After two years of operation the performance of 3D-Si pixel modules in terms of operation characteristics (signal,

Figure 12: 3D-Si sensors: hit efficiency as a function of bias voltage for different fluences and design variants [69].

noise, threshold settings, in-time efficiency) are on par with planar pixel modules operated with significantly higher voltages [68].

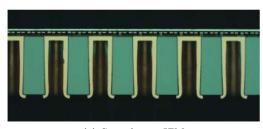

Current developments motivated by HL-LHC demands [69, 63, 70, 71] target the following goals to optimize radiation hardness, granularity, material budget, and processing costs [71]: (a) thin sensors ( $\sim 100 \, \mu \text{m}$ ) on 6" wafers, (b) narrower electrodes ( $\sim 5 \,\mu\text{m}$ ), (c) shorter electrode spacing ( $\sim 30 \,\mu\text{m}$ ), and (d) very slim  $(\sim 50 \,\mu\text{m})$  or active edges. Single sided processing is preferred providing cost benefits. An advanced design [71] is shown in fig. 11(c). A thin, highly resistive (p-type) sensor wafer is supported by a low ohmic  $(p^{++})$  handle wafer that can be backside thinned after processing. While the p<sup>+</sup> columns are deep etched through to the handle wafer where they receive their electric potential, the n<sup>+</sup> columns stop about 15 µm short from the handle wafer. In addition to cost and yield advantaged of single-sided processing, studies have shown that the tradeoff between signal efficiency and breakdown performance favors partial depth n-columns (not extending all the way through the thickness) [72]. At the top surface isolation of the n-columns is achieved by a p-spray layer preventing the electron accumulation layer underneath the oxide from creating shorts. Sensors are designed to meet the currently planned pixel area sizes of  $50 \times 50 \,\mu\text{m}^2$  or  $25 \times 100 \,\mu\text{m}^2$ , as shown on the right of fig. 11(c). The performance of such designs has been shown to yield high breakdown voltages before and after irradiation [73].

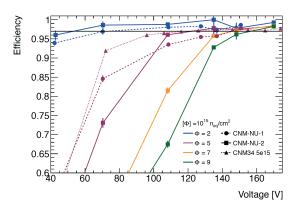

The hit efficiency obtained with 3D-Si structures designed by CNM [69] is demonstrated in fig. 12 for fluences of up to  $0.9 \times 10^{16} \,\mathrm{neq/cm^2}$  [69]. A >97% efficiency plateau is reached with comparatively low bias voltages of 150 V even at the highest fluences, with the missing 3% being largely due to tracks with straight incidence into the column structures, a case not possible for tracks from actual LHC collisions. Smaller implant pitches with lower voltages for the same field strength also reduce power dissipation due to leakage currents after irradiation. This creates some safety margin against thermal runaway, not completely negligible even at the moderate bias voltages of 3D-Si sensors [74].

3D-Si sensors therefore are a strong contender for hybrid pixel modules for the innermost pixel detector layers at the HL-LHC. It should be noted, however, that the fabrication process does is currently low volume. making it unlikely to cover large areas  $(> 1 \, \mathrm{m}^2)$  with this technology choice.

#### 3.3. Bonding techniques

Wafer- and chip-bonding as well as 3D-integration technologies are in wide-spread demand in the semiconductor industry sector of IC module assembly and stacking. Many techniques exist that are suitable for a large variety of applications and given fabrication constraints. A large amount of literature is available, reviewed and summarized for example in [75, 76, 77].

For hybrid pixel detectors, the mating of readout chips to substrate (sensor) plates or substrate wafers is the main application of bumping/flip-chipping and 3D-integration techniques. The overriding demands in these applications are small capacitance additions to the preamplifier by the bond connection, good yield with  $<10^{-4}$  defect rate (open or short), good contacts ( $<100\,\mathrm{m}\Omega$ ), and robustness against temperature cycling ( $-40^\circ\mathrm{C}$  to  $+60^\circ\mathrm{C}$ ). The need for small pitches between bond connections imposed a very high demand on industrial standards when pixel R&D for the LHC started. At the time the required pitch of 50 µm was about 15 years ahead of industrial demands. This pitch has become a standard today and requirements for current hybrid pixel R&D often target pitches less than 50 µm.

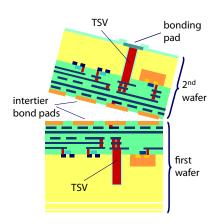

Bump or Under Bump Metalization (UBM, see below) application usually is a wafer-scale process. Flip-chipping, on the other hand, is conventionally employed to mate bumped readout chips to (bumped) sensor plates<sup>4</sup>. For the existing detectors at the LHC experiments and likely also for the upcoming upgrades, eutectic soldering<sup>5</sup> [78] and In-In thermocompression bonding are the methods that have been preferred over other techniques (see e.g. [1]) including anodic bonding, fusion bonding, and adhesive bonding (see below). In current techniques ICs are usually bonded to sensor plates or wafers (chip-to-wafer bonding, C2W). Wafer-to-wafer bonding (W2W) is a cost attractive future possibility for pixel detectors that might become interesting for applications in connection with further advances in vertical electrical interconnection in so-called 3D integration techniques. In particular through silicon vias (TSV) open the possibility to provide elegant and space efficient electrical contacts for hybrid pixel module fabrication when employing W2W or C2W bonding techniques. TSVs also allow reaching through to the backside of a chip (or sensor). This can be exploited to use the chip's backside metal for redistribution of readout or service lines (redistribution layer, RDL).

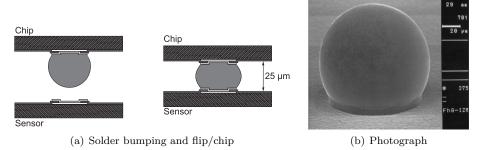

#### Solder bumps and bonding

One can perhaps subdivide the bonding technologies relevant in this review into (a) technologies requiring intermediate media to perform the bonding like for example eutectic bonding by means of solder or adhesive bonding using glue layers and (b) direct bonding, either metal-to-metal or silicon oxide-to-oxide. When intermediate materials are used no requirements on special surface treatments exist except for flatness. After UBM (and bump) fabrication, oxide removal is needed before flip-chipping can be done. The bonds are strong and

$<sup>^4</sup>$ Depending on the techniques one of the mating partners can have bumps as well, e.g. for In-In flip-chipping, or can just have UBM for the mating process, e.g. for solder bump flip-chipping.

<sup>&</sup>lt;sup>5</sup>Eutectic systems are solid mixtures that form a superlattice by striking a unique atomic percentage ratio and thus have the same melting point.

Figure 13: Eutectic solder bumps and the flip-chipping process: (a) Solder bump attached to a readout chip is bonded to the Under Bump Metalization of the pixel sensor; (b) SEM micrograph of a SnAg bump (courtesy of Fraunhofer IZM Berlin) .

post-processing - like thinning - is often possible. The lack of electrical connections (in the case of adhesive bonding) or price and pitch constraints (for solder bonding) are drawbacks.

The bonding technique currently used most often is the electrochemical application of solder micro bumps to either of the mating parts: chip or sensor (fig. 13). A description of the method and the process steps is given in [1]. Solder bumping was introduced in 1969 by IBM in the C4-process (Controlled Collapse Chip Connection) [59]. The process is still in use by CMOS vendors and is often offered with CMOS wafer production as an add-on. The pitch of the applied bumps is limited to 170  $\mu$ m or larger, often too large for fine-pitch, high granularity pixel detectors in particle physics. However, price and reliability arguments render C4-bumping still very attractive for low cost, large area applications at LHC upgrades, as is for example addressed in section 3.1.

Eutectic solder bumping has meanwhile been developed with high connection density down to pitches of  $25 \,\mu \text{m}$  [79] and bump dimensions of  $(15 \,\mu \text{m})^3$ . High yield is obtained with Sn/Pb as well as with lead free Sn/Ag or Au/Sn alloys [80]. The ultimate pitch limit is believed to be around 5–10 µm [25]. Readout ICs typically have Al or Cu pads for bump connection bounded by a passivation layer for chip protection. Typically a thin (100 nm) Ti:W layer is first sputtered onto the wafers to promote adhesion and provide a barrier to prevent Cu atoms from diffusing into the pad metal (Al). Then a Cu or Au plating base (> 150 nm)is applied for the electrochemical contact followed by a well wettable Cu layer  $(1-5 \,\mu\text{m})$ . This layer stack is the UBM and is applied to both mating parts. In a wafer-based process cylinders of an electrodeposit are now grown onto the UBM of one part and turned into a spherical shape by reflow. Bonding of both parts is so far mostly done after dicing of bumped readout ICs and sensor plates or wafers supplied with UBM in a flip-chipping process and subsequent re-melting of the solder bumps. Note that this reflow process provides self-alignment of the mated parts.

Eutectic solder bumping is regarded as present day's workhorse bonding technique for hybrid pixel detectors. For the ATLAS pixel detector very high bond yields of more than 99% have been obtained (i.e. number of modules not rejected due to bonding issues).

(a) Indium bumps (flat)

(b) Photograph

Figure 14: In-In bonding: indium bumps produced before (a) and after (b) reflow to a sphere (from [1], courtesy of S. Ritter, PSI).

#### In-In bonding

In-In bonding has also been used in LHC pixel detectors for a large quantity of pixel modules. The technique usually employs vapour deposition<sup>6</sup> of indium through openings in the lift-off masks deposited on the wafer (see e.g. [1]). The mask is pulled off from the wafer by a wet lift-off process, requiring the bumps to be fairly flat and thin ( $\approx 10 \, \mu m$ , fig. 14(a)). Also a UBM is necessary for this process, usually Ti-Pt-(Au) is used. The applied indium bumps are then bonded by thermocompression at about 100 °C. The advantages of the technique are its ease of application and the low temperature requirements. The bonds are, however, comparatively fragile, and the fabricated modules tend to have a lower mechanical damage threshold than solder bumped assemblies. In the Run-1 ATLAS pixel detector about 50% of the modules were produced using In-In bonding, showing high reliability with acceptance yields around 90%. For the CMS pixel detector a reflow step has been introduced after bump deposition [81], turning the In bumps into spherical shapes (fig. 14(b)). The two spheres are merged in a second reflow at 180 °C. This provides a larger distance between chip and sensor, but it introduces self-alignment and stronger bonds.

#### Adhesive bonding

Recently adhesive wafer-to-wafer bonding has been discussed in the context of active CMOS sensors, capacitively coupled to readout chips where the capacitive coupling is provided between the metal pads of sensor and chip, respectively, separated by the adhesive bonding layer. Adhesive bonding has been claimed to reduce production cost by avoiding the UBM, bump deposition, and reflow steps. This has, however, not yet been demonstrated and is not at all obvious. Planarity requirements are stricter and requirements for alignment for chip-to-chip/sensor placement are the same as for standard bump bonding, the latter being the cost driver, not to mention the need for (cost intensive) electrical connections of the mated parts if provided by TSVs.

In the context of capacitive coupling of 'smart sensors' to readout ICs (CCPD) adhesive bonding has been investigated regarding thickness control and uniformity of the adhesive as well as radiation tolerance [82]. Good glue unifor-

<sup>&</sup>lt;sup>6</sup>electroplating of indium is also possible

mity at the micrometer level has been achieved, however further evaluation of its competitiveness is needed, in particular whether electrical connections can be provided by cheap techniques like e.g. wire bonding, thus, however, abandoning the goal of compact module shapes.

#### Cu-Cu direct bonding

Metal-metal adhesion (Cu-Cu or Au-Au) of flat and polished surfaces has been known for a long time. The bonding forces principally involve capillary, Van der Waals, and electrostatic forces, as well as solid bridges caused by impurities and hydrogen bonds between OH groups.

Two mirror-polished wafers are put into contact and held together by adhesive forces without any intermediate material [75]. The process completes by Cu atom diffusion between the two Cu layers. Thermocompression (diffusion) bonding is simplest, but the required temperatures are usually too high for typical sensors and CMOS chips used in pixel detector applications.

Especially interesting is surface-activated Cu-Cu bonding as it works at ambient temperature. Surface-activation in this context means increasing the bonding force by surface treatment, e.g. by augmenting the number of hydrogen bonds (hydrophilicity) or by generating new types of chemical bonds. The treatment methods comprise wet chemical processes and (oxygen) plasma etching. The bonds are electrically conductive, an advantage for any wafer-to-wafer but also chip-to-wafer bonding project.

Requirements for good bonding are native oxide and other remnant removal, excellent chemical-mechanical polishing (CMP), and highly planar parts (wafers) with sufficient total Cu fraction. Very fine pitch ( $<4\,\mu m$ ) and low capacitance contacts are possible. The demands on surface cleanliness and flatness are the biggest drawbacks. Wafers must be processed soon after fabrication. Wafers must be very planar and sufficiently stiff which might compromise very thin solutions. At present the technique is also still fairly expensive.

#### Oxide-oxide direct bonding

Under room temperature conditions silicon wafers are covered with an oxide layer that can be used for direct wafer bonding, a method commonly used for SOI wafer production. Most common is 'hydrophilic' wafer bonding in which the wafers are, after cleaning, rinsed or stored in deionized water. Water is bonded via Si-OH groups on the silica surface. The bonding can be done at room temperature but the bonding strength increases with temperature (and time). With the addition of an electric field one speaks of anodic bonding, which can tolerate rougher surfaces.

Required is high quality CMP polishing and extremely good surface cleaning to avoid large bonding voids. The bonds are non-electrical. Hence TSVs or other electrical connections are needed for pixel assemblies. For this process wafer-to-wafer bonding is much easier than chip-to-wafer or chip-to-chip.

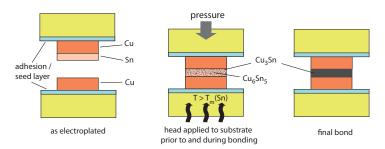

### Solid-liquid interdiffusion bonding (SLID)

SLID bonding uses an intermetallic alloy formation and represents an alternative fine-pitch bonding technique based on thin (often eutectic) Cu-Sn connects [83, 75]. Between two Cu layers of several micron thickness a thin  $(3 \mu m)$  Sn layer is applied on one of the Cu layers (fig. 15). They are brought in contact

Figure 15: Process steps of Solid-Liquid Interdiffusion bonding (SLID): (a) structure with metal stacks before bonding, (b) alloy forming step under pressure at 240-320 °C, (c) resulting bond connection.

and heated to a temperature of around 240–320 °C. At this temperature the tin diffuses into the copper forming the Cu-Sn alloy. As the melting point of this alloy is around 600 °C multiple layers can be stacked and connected without melting the previously formed SLID connections. Furthermore, the process is also a flux-free bonding alternative with pitches much below 20  $\mu m$ , whereas the number of processing steps is about the same as for solder bonding (the reflow step is not needed). Technically, for SLID, pressure and temperature are required during the bonding step. This renders sequential bonding of multi-chip pixel modules necessary (chip after chip), whereas bonding by reflow does not require pressure (c.f. page 23) and can be done in parallel for a number of chips bonded to a sensor plate.

Despite their similarity SLID and soldering are fundamentally different processes with distinct and unique properties. A major difference is that soldering is reversible, whereas SLID is irreversible and only melts at temperatures much higher than the SLID process temperature. This implies also that no reworking is possible. Some process similarities to metal-metal thermocompression bonding also exist. A detailed comparison is given in [75]. SLID is particularly suited for wafer-to-wafer and chip-to-wafer bonding.

#### 3.4. Wafer thinning

Thin wafers are a goal not only for low-mass pixel detectors in particle detection, but also for a number of integration processes, in particular for Through-Silicon Vias. While thick wafers are better for handling, other process steps like for example etching benefit from small wafer thickness. However, dedicated 'handling wafers' are needed to deal with flatness and bowing issues. Often handling wafers are of the SOI (Silicon-on-Insulator) type, because the Si-SiO $_2$  interface transition offers a sharp etch stop with the oxide also acting as a sacrificial layer after ion etching.

Wafers are thinned by (backside) grinding. The active (front) side is first protected by tape. Grinding in two steps (coarse/fine) is performed using grinding wheels with diamond grain sizes from 1-8  $\mu$ m (fine) to 20-80  $\mu$ m (coarse) diameter. After the thinning process, breaking strength, warpage, and bow are characterization parameters that depend on the grinding tool characteristics and the grinding speed. More details are given in [76].

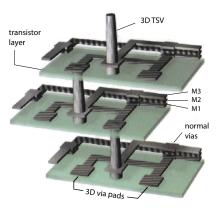

- (a) Device layers connected by TSVs

- (b) Bonding of two wafers with electrical connection via a SuperContact TSV.

Figure 16: 3D-integration principle: (a) TSVs connecting different electronics device layers (adapted from [76]); (b) bonding of two wafers with electrical SuperContacts to the outside (Tezzaron; adapted from [84]).

#### 3.5. 3D-integration and through-silicon vias

Extending electronics integration into the third dimension is - apart from feature size shrinking - regarded as the second route to ever increasing circuit density. 3D-stacking of several electronic device layers (tiers) is thus an eminent field of industrial research. Further advantages are reduced power consumption due to smaller connections and smaller involved capacitances as well as larger I/O bandwidth and more functionality at lower cost. Vertical vias running through layers of silicon (TSVs) are a key ingredient for 3D-stacking [76]. Tiers can be different CMOS layers but also electronics and sensor layers or layers interfacing to an optical signal transport. Figure 16(a) is a sketch illustrating the principle of 3D-interconnection via TSVs.

Besides TSV fabrication, wafer thinning and aligned wafer bonding are the key follow-up processes for 3D-integration. Direct bonding, especially Cu-Cu fusion or SLID (see above) are the preferred bonding techniques for 3D-stacking, providing strong fine-pitch bonds that are also conductive.

For future pixel detectors in particle physics, 3D-integration and TSVs are of interest if (a) wafer scale production becomes practical and/or (b) if TSVs allow better connectivity of detector modules by avoiding space consuming wire bonds and providing better buttable modules. In addition TSVs can reach through to the backside of a chip, allowing redistribution of electrical connections on the chip's backside metal is addressed. This in turn saves the material normally added by flex interconnect circuits.

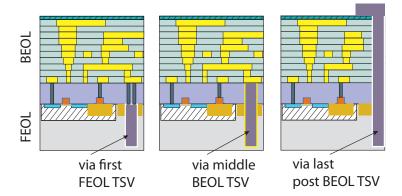

Figure 17: Different types of vias. (left) via-first: fabrication before or during FEOL, (middle) via-middle: fabrication after FEOL during BEOL, (right) via last fabrication after IC completion (post-BEOL) (adapted from [85]).

#### TSV fabrication

In IC fabrication all processes before the first wiring metal are called *front* end of line (FEOL), whereas the back end of line (BEOL) begins with this first metal processing and ends with the last IC processing step. Different types of TSVs are distinguished depending on the point in the process flow at which they are fabricated [87], i.e.

- via-first or FEOL via (polysilicon) applied before or during FEOL fabrication

- via-middle or BEOL via (metal) applied after FEOL during BEOL fabrication

- via-last or post-BEOL via(metal) applied after IC fabrication post-BEOL. Here one distinguishes also front side via-last as in fig. 17 (right) and backside via-last, depending on whether the via is etched from the front through the BEOL stack (difficult) or from the back through (thinned) silicon substrate.

Note that the conducting material for FEOL TSVs must be doped polysilicon for reasons of thermal and material compatibility, having the disadvantage of higher resistivity compared to metals. For BEOL and post-BEOL vias tungsten and copper are most common. Figure 17 shows these distinct TSV types schematically.

Important TSV specifications are diameter, pitch, and aspect ratio (length-diameter ratio). Present typical ranges are given in table 2.

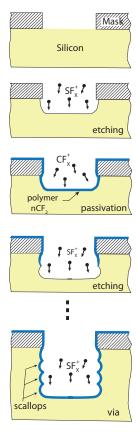

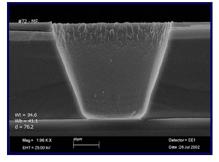

The main process for TSV production is deep reactive ion etching (DRIE, invented by Bosch [86]). The process employs a directional repetitive sequence of ion etching and wall passivation resulting in anisotropic etching of the silicon bulk. The principle is shown in fig. 18. The alternating cycles (typically lasting about 5 s) are: etching under a bias voltage with SF<sub>6</sub> or NF<sub>3</sub> in argon atmosphere to form gaseous  $SiF_x^+$  products - passivation of the surfaces with  $C_3F_6$ ,  $C_4F_8$ , or CHF<sub>3</sub> in argon forming a protecting fluorocarbon polymer surface layer on sidewalls and bottom. The bias voltage provides a directional orientation of the

Figure 18: Deep Reactive Ion Etching (DRIE) in the Bosch process [86]. From top to bottom a sequence of ion etching and passivation is executed (see text).

| via type            | smallest diameter    | smallest pitch       | typical aspect ratio |

|---------------------|----------------------|----------------------|----------------------|

| via-first           | $3-5~\mu m$          | $6 - 10 \; \mu m$    | 10:1                 |

| via-middle          | $3-5~\mu\mathrm{m}$  | $6-10~\mu\mathrm{m}$ | 5-10:1               |

| front side via-last | $10 - 20 \; \mu m$   | $20 - 40 \; \mu m$   | 5:1                  |

| backside via-last   | $5-20~\mu\mathrm{m}$ | $10 - 40 \; \mu m$   | 5-12:1               |

Table 2: Typical TSV parameters (2017) [76, 87, 88].

bombardment. The resulting via has a typical scalloped surface with undercuts that are, however, substantially reduced by advanced DRIE parameters.

## First HEP experiences with TSVs

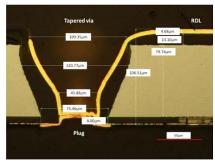

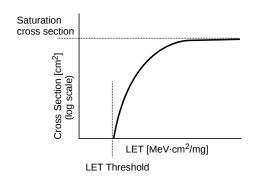

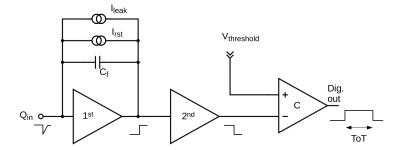

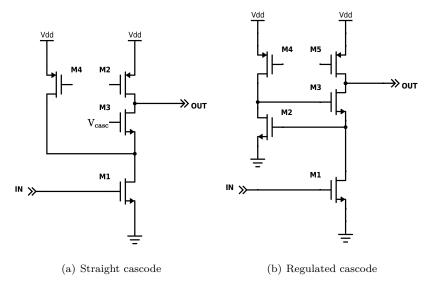

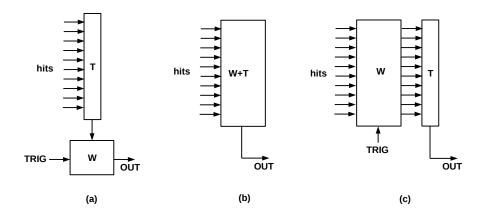

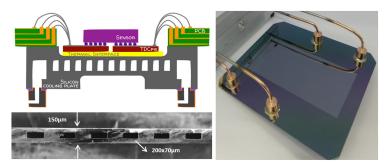

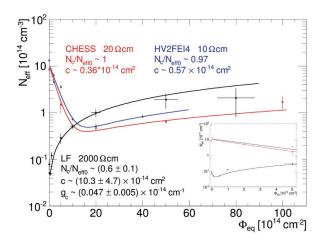

A characteristic of TSV application for HEP pixel detectors is the fact that readout chips or sensors are still comparatively thick (100-200  $\mu m)$  for via fabrication. On the other hand the required via pitch and density often is relaxed, for example when only service lines need to be via-connected or when I/O pads can have large pitches.