# HiHGNN: Accelerating HGNNs through Parallelism and Data Reusability Exploitation

Runzhen Xue, Dengke Han, Mingyu Yan, *Member, IEEE*, Mo Zou, Xiaocheng Yang, Duo Wang, Wenming Li, Zhimin Tang, John Kim, *Senior Member, IEEE*, Xiaochun Ye, and Dongrui Fan, *Senior Member, IEEE*

Abstract—Heterogeneous graph neural networks (HGNNs) have emerged as powerful algorithms for processing heterogeneous graphs (HetGs), widely used in many critical fields. To capture both structural and semantic information in HetGs, HGNNs first aggregate the neighboring feature vectors for each vertex in each semantic graph and then fuse the aggregated results across all semantic graphs for each vertex. Unfortunately, existing graph neural network accelerators are ill-suited to accelerate HGNNs. This is because they fail to efficiently tackle the specific execution patterns and exploit the high-degree parallelism as well as data reusability inside and across the processing of semantic graphs in HGNNs.

In this work, we first quantitatively characterize a set of representative HGNN models on GPU to disclose the execution bound of each stage, inter-semantic-graph parallelism, and inter-semantic-graph data reusability in HGNNs. Guided by our findings, we propose a high-performance HGNN accelerator, HiHGNN, to alleviate the execution bound and exploit the newfound parallelism and data reusability in HGNNs. Specifically, we first propose a bound-aware stage-fusion methodology that tailors to HGNN acceleration, to fuse and pipeline the execution stages being aware of their execution bounds. Second, we design an independency-aware parallel execution design to exploit the inter-semantic-graph parallelism. Finally, we present a similarity-aware execution scheduling to exploit the inter-semantic-graph data reusability. Compared to the state-of-the-art software framework running on NVIDIA GPU T4 and GPU A100, HiHGNN respectively achieves an average 40.0× and 8.3× speedup as well as 99.59% and 99.74% energy reduction with quintile the memory bandwidth of GPU A100.

Index Terms—Heterogeneous graph neural network, Graph neural network, HGNN accelerator, GNN accelerator, HGNN, GNN.

# 1 Introduction

ANY real-world data in complex systems are naturally represented as heterogeneous graphs (HetGs), which possess not only structural information but also rich semantic information [48]. HetGs consist of multiple types of entities and relations which are embodied by various types of vertices and edges, respectively. This is the major difference of that with homogeneous graphs (HomoGs), which contain only a single type of vertices and edges and thus only represent structural information. Due to the powerful representation ability of HetG, it has been widely adopted in many critical fields such as knowledge graph [9], [43], [49], [76], social network [54], [72], [79], [80], and many others.

Heterogeneous graph neural networks (HGNNs) originate from the insufficiency of using graph neural networks (GNNs)

to process HetGs' semantic information. Designed for HomoGs to capture their structural rather than semantic information, GNNs recursively aggregate the feature vectors of neighboring vertices [28], [35], [64] to generate the final embedding vector for each vertex. In contrast, HGNNs use a different execution semantic to capture both pieces of information. They usually can be partitioned into four major execution stages [40], [47], [58], [62], [71]: (1) Semantic Graph Build (SGB) stage partitions the original HetG into several semantic graphs; 2 Feature Projection (FP) stage transforms the feature vector of each vertex in each semantic graph to a new one using a multi-layer perceptron (MLP); (3) Neighbor Aggregation (NA) stage aggregates features from neighbors for each vertex in each semantic graph; (4) Semantic Fusion (SF) stage fuses semantic information revealed by all semantic graphs, i.e., fuses the results of the NA stage across different semantic graphs for each vertex. HGNNs have achieved excellent prediction accuracy in the processing of HetG and become at the heart of a broad range of critical fields [10], [61], [70], [78] such as recommendation systems [11], [29], medical analysis [39], knowledge inference [3], [55], [60], malicious account detection [38], information retrieval [41], shop search [42], etc.

Deriving from the above workflow, HGNNs exhibit different performance bottlenecks and new acceleration opportunities, compared with GNNs. According to our quantitative characterization, different stages of HGNNs face different execution bounds, causing low utilization of compute and memory components. In addition, HGNNs earn the opportunity to exploit the high-degree parallelism and data reusability in the parallel processing of semantic graphs, which brings the possibility to improve overall

<sup>•</sup> Runzhen Xue, Dengke Han, Mingyu Yan, Duo Wang, Wenming Li, Zhimin Tang, Xiaochun Ye, and Dongrui Fan are with the State Key Lab of Processors, Institute of Computing Technology, Chinese Academy of Sciences, Beijing 100045, China, and also with the University of Chinese Academy of Sciences, Beijing 101408, China. Mingyu Yan is also with the Shanghai Innovation Center for Processor Technologies, Shanghai 201203, China. E-mail: {xuerunzhen21s, handengke21s, yanmingyu, wangduo18z, liwenming, tang, yexiaochun, fandr}@ict.ac.cn.

Mo Zou and Xiaocheng Yang are with the State Key Lab of Processors, Institute of Computing Technology, Chinese Academy of Sciences, Beijing 100045, China E-mail: {zoumo, yangxiaocheng}@ict.ac.cn.

John Kim is with the School of Electrical Engineering, Korea Advanced Institute of Science and Technology, Daejeon 305701, Korea. E-mail: jjk12@kaist.ac.kr.

Runzhen Xue and Dengke Han contributed equally to this work. Mingyu Yan is the corresponding author of this paper.

performance and efficiency.

Unfortunately, existing GNN accelerators lack the HGNN-oriented design and optimization to efficiently accelerate HGNNs. In particular, a stage-fusion methodology specific to the execution semantics of HGNNs is missed in their designs [15], [66], to improve the utilization of hardware components. Besides, they fail to efficiently exploit the high-degree inter-semantic-graph parallelism and data reusability in the processing of HGNNs.

In this work, we quantitatively characterize a set of representative HGNN models on GPU to ferret out the execution patterns, performance bottlenecks, and acceleration opportunities of HGNNs. Guided by the characterizations, we design a highperformance HGNN accelerator, called HiHGNN, to exploit the newfound parallelism and data reusability in HGNNs. Specifically, we first propose a novel stage-fusion methodology tailoring to HGNNs, called bound-aware stage fusion. It decomposes and reorganizes coarse-grained stages of HGNNs into fine-grained stages with explicit execution bounds, enabled by a stage-fusion programming model. Then, these fine-grained stages are fused and allowed pipelined execution through a stage-fusion hardware datapath, ensuring higher compute and memory utilization. Second, we propose an independency-aware parallel execution design to exploit the inter-semantic-graph parallelism. This design is built by a multi-lane architecture equipped with workload-aware scheduling, which exploits the high-degree parallelism exposed by the independencies between the processing of semantic graphs, thereby additional hardware resources can be added to further improve performance. Third, we propose a similarity-aware execution scheduling to harness the potential inter-semantic-graph data reusability. The degree of data reusability between semantic graphs is proportionate to their similarity. To leverage this insight, we construct a hypergraph by taking each semantic graph as a vertex and the similarity between them as edge weights. By conducting the shortest Hamilton path algorithm on this hypergraph, we generate an execution order for the semantic graphs to maximally exploit the inter-semantic graph data reusability.

To summarize, we list our contributions as follows:

- We conduct a quantitative characterization of HGNNs on GPU to uncover the execution patterns, performance bottlenecks, and acceleration opportunities of HGNNs.

- We propose a high-performance HGNN accelerator, called HiHGNN, to alleviate performance bottlenecks and exploit the newfound parallelism and data reusability in HGNNs.

- We propose a bound-aware stage fusion methodology that tailors to HGNN acceleration, including a novel programming model and hardware datapath. Moreover, we propose an independency-aware parallel execution and a similarity-aware execution scheduling to respectively exploit the inter-semanticgraph parallelism and data reusability.

- We implement HiHGNN in RTL and evaluate it through a

detailed microarchitectural simulation and on FPGA. Compared

to the state-of-the-art software framework running on NVIDIA

GPU T4 and GPU A100, HiHGNN achieves an average 40.0×

and 8.3× speedup as well as 99.59% and 99.74% energy

reduction, respectively.

# 2 BACKGROUND

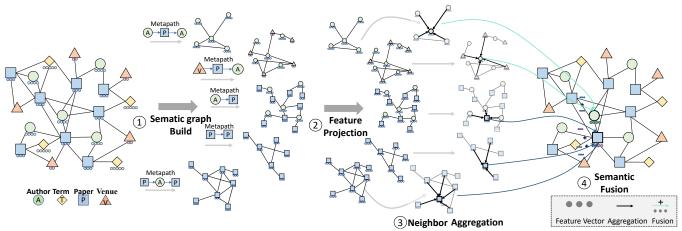

In this section, we introduce the relevant concepts for HGNNs using Table 1, Fig. 1, Algorithm 1, and Table 2.

TABLE 1 Notations and corresponding explanations.

| Notation         | Explanation                      | Notation                             | Explanation              |

|------------------|----------------------------------|--------------------------------------|--------------------------|

| G                | heterogeneous graph              | V                                    | vertex set               |

| $\boldsymbol{E}$ | edge set                         | $\mathscr{T}^{v}$                    | vertex type set          |

| $\mathscr{T}^e$  | edge type set                    | u, v                                 | vertex                   |

| $e(e_{u,v})$     | edge (from $u$ to $v$ )          | $G^{\mathscr{P}}$                    | semantic graph           |

| r, P             | relation, metapath               | $c(c_v)$                             | vertex type              |

| h                | vertex or relation embedding     | $\mathscr{N}_{v}$                    | neighbor set of vertex v |

| W                | transformation weight matrix     | h'                                   | projected vertex feature |

| a                | attention vector                 |                                      | concatenation            |

| $\alpha_{u,v}$   | attention importance             | $\theta(\theta_{u,v}^{\mathscr{P}})$ | attention coefficient    |

| z                | intermediate aggregation feature | b                                    | transformation bias      |

| σ                | non-linear functions             | x                                    | original vertex feature  |

|                  |                                  |                                      |                          |

### **Algorithm 1: HGNN Programming Model**

```

1 for each vertex v do

h'_{v}=Feature Projection(h_{v});

3 end

for each semantic graph G^{\mathcal{P}} do

for each vertex pair (u, v) do

z_{v}^{\mathscr{P}}=Neighbor Aggregation(h'_{u});

end

8 end

for each vertex v do

for each semantic graph G^{\mathcal{P}} do

z_{\nu}=Semantic Fusion(z_{\nu}^{\mathscr{P}});

11

12

end

13 end

```

**Heterogeneous Graph.** A HetG shown in Fig. 1, is defined as  $G = (V, E, \mathcal{T}^v, \mathcal{T}^e)$  [40], [71] using notations in Table 1, where V is the set of vertices with a vertex type mapping function  $\phi: V \to \mathcal{T}^v$ , and E is the set of edges with an edge type mapping function  $\psi: E \to \mathcal{T}^e$ . Each vertex  $v_i \in V$  is attached with a vertex type  $c_v = \phi(v_i) \in \mathcal{T}^v$ . Each edge  $e_{u,v} \in E$  is attached with a relation  $r_{c_v,c_u} = \psi(e_{u,v}) \in \mathcal{T}^e$ , starting from the source vertex u to the target vertex v. A graph is heterogeneous when  $|\mathcal{T}^v| + |\mathcal{T}^e| > 2$ , otherwise it is homogeneous.

**Semantic Graph.** The semantic graph is generated by different metapath. A metapath refers to a sequence of vertex types and edge types that captures specific semantic relationships between vertices. It provides a higher-level abstraction of the graph structure and enables the identification of meaningful paths and patterns within the graph. By defining and utilizing metapaths, we can gain insights into the complex relationships and dependencies present in HetGs. For example in Fig.1, a HetG is partitioned into several semantic graphs based on metapaths [52], [53], such as author—paper—author (abbreviated as APA) that represents a coauthor relationship.

Heterogeneous Graph Neural Network. HGNN follows a neighborhood aggregation scheme and a semantic fusion scheme, where the final representation of each vertex is computed by recursively aggregating the feature vectors of its neighbor vertices in each semantic graph and fusing the aggregated results across all semantic graphs, as shown in Fig. 1. For example, HAN [62] aggregates structural information using the neighbor attention in each semantic graph and then fuses outputs from different semantic graphs using the semantic attention for each vertex.

To capture both the structural information and semantic information in HetGs, most prevalent HGNN models usually contain four major execution stages as shown in Fig. 1. ① Semantic Graph Build: The SGB stage builds semantic graphs for the following stages by partitioning the original HetG into a set

Fig. 1. Illustration of HGNNs.

TABLE 2

The illustration of representative HGNN models.

|                         | HAN [62]                                                                                                                           | R-GAT [58]                                                                                                                            | R-GCN [47]                                                                               | S-HGN [40]                                                                                                                                                                            |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Feature<br>Projection   | $h_{\nu}' = W^{c_{\nu}} x_{\nu}$                                                                                                   | $h_{v}^{r}=W^{r}x_{v}$                                                                                                                |                                                                                          | $h_{\nu}' = W^{c_{\nu}} x_{\nu}$                                                                                                                                                      |

| Neighbor<br>Aggregation | $\sum_{k \in \mathscr{N}_{v}} \exp(\theta_{v,k}^{\mathscr{S}})^{\vee v} \qquad ( = u \in \mathscr{N}_{v}^{\mathscr{S}}  u, v  u )$ |                                                                                                                                       | $z_{v}^{r} = \frac{1}{ \mathcal{N}_{v}^{r} } \sum_{u \in \mathcal{N}_{v}^{r}} h_{u}^{r}$ | $\alpha_{u,v} = \frac{\exp(\sigma(a^T[h'_u  h'_v  W_rh_r]))}{\sum_{k \in \mathcal{N}_v} \exp(\sigma(a^T[h'_k  h'_v  W_rh_r]))},$ $h_v = \sum_{u \in \mathcal{N}_v} \alpha_{u,v} h'_u$ |

| Semantic<br>Fusion      | $w = \frac{1}{1-2} \sum_{u \in V} g q^T \cdot \tanh(W^{\mathscr{P}} z_u^{\mathscr{P}} + b),$                                       | $h_{\scriptscriptstyle \mathcal{V}} = rac{1}{ \mathscr{P} } \sum_{\mathscr{P}_i} z_{\scriptscriptstyle \mathcal{V}}^{\mathscr{P}_i}$ | $h_{\nu} = \sum_{r} z_{\nu}^{r} + W^{c_{\nu}} x_{\nu}$                                   | _                                                                                                                                                                                     |

of semantic graphs based on relations or predefined metapaths.

② Feature Projection: In the FP stage, the feature vector of each vertex is transformed to a new one using a MLP within each semantic graph. ③ Neighbor Aggregation: The NA stage utilizes an attention mechanism [56] to perform a weighted sum aggregation of features from neighbors within each semantic graph. ④ Semantic Fusion: The SF stage fuses the semantic information obtained from all semantic graphs with an attention mechanism [56], aiming to combine the results of the NA stage across different semantic graphs for each vertex. Algorithm 1 shows the programming model for HGNNs. Table 2 presents the computation corresponding to each stage of four representative HGNN models.

### 3 MOTIVATION

This section explains the motivation to design the accelerator for HGNNs via characterization.

### 3.1 Characterization of HGNNs on GPU

We conduct a quantitative characterization for HGNNs on an NVIDIA GPU T4 using two prevalent HGNN models. We focus on the last three stages for the inference acceleration on transductive learning and omit SGB stage since it is executed in CPU in the training phase. The experimental setup is shown in Section 5. Note that the processing of total vertices is batched into a coarse-grained matrix operation for efficient execution on GPUs.

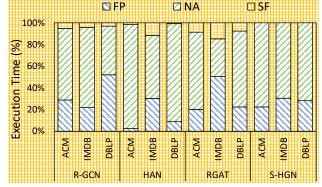

**Execution Time Breakdown.** Fig. 2 shows the breakdown of the execution time of the inference phase. The FP, NA, and SF stages take 26.5%, 68.7%, and 4.8% execution time averaging across different models and datasets, respectively. For S-HGN, since the SF stage is replaced by the edge embedding, there is no explicit SF stage in the execution. From above, the NA stage

Fig. 2. Execution time breakdown.

dominates the execution time of HGNNs. The reason is that, for each semantic graph, neighboring feature vectors of each vertex in the corresponding semantic graph need to be aggregated, which is time-consuming.

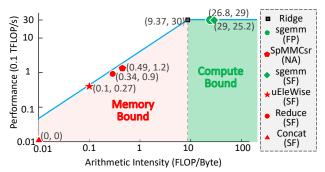

**Execution Bound.** Different stages exhibit different execution bounds, leading to low utilization of various hardware components, as demonstrated in Fig. 3 and Table 3.

- The FP stage is dominated by the execution of dense-dense matrix multiplication, primarily facing compute bound. The CUDA kernels in the FP stage generally exhibit compute bound due to their high compute-to-memory-access ratios, such as the sgemm (dense-dense matrix multiplication) kernel. For example, the sgemm kernel in the HAN model on the DBLP dataset costs over 97.4% execution time of the FP stage and achieves 95.9% peak performance while the DRAM bandwidth is underutilized with only 33.6%. The arithmetic intensity of this kernel is 26.8 FLOP/Byte and larger than the one in the ridge of Roofline (see Fig. 3), which reveals that the FP stage faces compute bound.

- The NA stage is dominated by the execution of graph-

Fig. 3. CUDA kernels in the floating-point operation Roofline of GPU T4 on HAN model with DBLP dataset.

TABLE 3

Profiling results of major CUDA kernels on HAN model with DBLP dataset.

| Kernel<br>Name                                 | Time (%)            | Achieved Peak<br>Performance (%)      | DRAM Bandwidth<br>Utilization (%) | L2 Cache<br>Hit Rate (%)              |  |

|------------------------------------------------|---------------------|---------------------------------------|-----------------------------------|---------------------------------------|--|

|                                                | C                   | 2) Feature Projection                 | (Compute Bound)                   |                                       |  |

| sgemm                                          | 97.4%               | 95.9%                                 | 33.6%                             | 82.7%                                 |  |

| ③ Neighbor Aggregation (Memory Bound)          |                     |                                       |                                   |                                       |  |

| SpMMCsr 85.9% <b>3.9</b> % 74.3% <b>31.4</b> % |                     |                                       |                                   |                                       |  |

| 4                                              | Seman               | tic Fusion (Compute                   | Bound → Memory B                  | Sound)                                |  |

| sgemm<br>uEleWise<br>Reduce                    | 47.8%<br>20%<br>11% | 84.2%<br><b>0.9</b> %<br><b>3.1</b> % | <b>42.4%</b><br>82.4%<br>88.3%    | 83.3%<br><b>50.0%</b><br><b>25.2%</b> |  |

| Concat                                         | 17.5%               | 0%                                    | 81.6%                             | 50.0%                                 |  |

topology-dependent operations, primarily exhibiting memory bound and irregular memory access pattern. The CUDA kernels in the NA stage perform compute operations dependent on the irregular topology of graphs, generally showing memory bound caused by the irregular memory accesses to neighboring feature vectors, such as the SpMMCsr (SpMM, sparse-dense matrix multiplication). Taking the HAN model on the DBLP dataset as an example, the SpMMCsr kernel aggregates neighboring feature vectors into a single vector for each vertex according to the irregular neighbor connection. This kernel achieves high DRAM bandwidth utilization (74.3%) with a low L2 Cache hit rate (31.4%) due to the intensive irregular memory accesses. Nevertheless, this kernel exhibits low arithmetic intensity (0.49 FLOP/Byte) and low achieved peak performance (3.9%). This reveals that many computing resources in the NA stage are underutilized.

• The SF stage is dominated by the execution of densedense matrix multiplication, element-wise operation, and data rearrangement operation, primarily facing compute bound first and then memory bound. In this stage, the sgemm kernel first calculates attention weights for each resulting feature vector of each semantic graph from the NA stage, and then the uEleWise (unrolled\_elementwise\_kernel), Concat (CatArrayBatchedCope) and Reduce kernels aggregate these feature vectors into single one for each vertex with attention weights. The sgemm kernel still exhibits compute-bound as the high peak performance (84.2%). On the contrary, the uEleWise, Reduce, and Concat kernels show memory bound, which achieve over 80% DRAM bandwidth utilization with minor peak performance. As a result, the SF stage faces low DRAM bandwidth utilization first and then low compute utilization as well as low L2 Cache hit rate.

**Differences between GNNs and HGNNs.** The major differences between GNNs and HGNNs on execution are:

- Joint Feature Projection vs. Separate Feature Projection. The raw feature vector of each vertex in HomoGs is in the same vector space with the same dimension. Thus, the feature projection of vertices in GNNs can be performed jointly. However, the raw feature vectors of vertices of different types in HetGs are not in the same vector space and have different dimensions, requiring different feature projection parameters. Generally, HGNNs utilize a specific feature projection matrix for each vertex type or in each semantic graph.

- Aggregation vs. Aggregation+Fusion. GNNs only aggregate once for the neighbor aggregation on a single type of relation. HGNNs aggregate features from neighbors in each semantic graph generated according to corresponding semantics (relations or metapaths), and then fuse intermediate results of each semantic graph for each vertex.

These differences introduce high-degree inter-semantic-graph parallelism and data reusability, exposing opportunities for HGNN acceleration. The inter-semantic-graph parallelism in the NA stage points to that different semantic graphs can be processed in parallel. The inter-semantic-graph data reusability derives from that the intermediate results of the FP stage can be reused across the processing of different semantic graphs. Furthermore, more semantic graphs can capture more semantics in deep, which helps improve the prediction accuracy of HGNNs [71]. It follows that these parallelism and data reusability becomes higher degree as the number of metapaths increases.

#### 3.2 The Need for an HGNN Accelerator

Given the above characterizations, we explain the motivation to design an HGNN accelerator.

Limitations of GNN Accelerators. GNN accelerators tailored to GNNs gain significant speedup and energy savings compared to GPUs [7], [15], [66]. Whereas, they lack the HGNN-oriented design and optimization to accelerate HGNNs. First, they have proposed stage-fusion optimizations to accelerate GNNs, but they are ill-suited to HGNNs. This is because the execution semantics and execution patterns of the sequential stages in HGNNs differ from those in GNNs, resulting in different fusion methodologies of compute, memory access, and dataflow. Second, they miss elaborate optimizations to exploit the high-degree inter-semantic-graph parallelism and data reusability in the processing of HGNNs. Third, GNNs and HGNNs have great differences in execution patterns. GNN accelerators lack the control unit to schedule the whole execution for HGNNs.

Inefficiencies of GPUs. GPUs are inherently tailored to compute-intensive workloads such as dense-dense matrix multiplication [36]. GPUs cannot efficiently handle irregular memory accesses caused by the graph-topology-dependent execution pattern in the NA stage [2], [19], [50], [65], [66], [67], [68], suffering from low efficiency. For example, the SpMMCsr kernel in the NA stage exhibits high DRAM bandwidth utilization with a low L2 Cache hit rate (see Section 3.1). This reveals that frequent replacements of feature vectors have occurred, which introduce many redundant DRAM accesses. In addition, existing software frameworks usually execute stages with different execution bounds in serial to leverage hardware-optimized coarse-grained operations on GPUs [12], [59] (e.g., SpMM), causing low compute utilization and DRAM bandwidth utilization.

**Design Requirements.** Given the characteristics of HGNNs, we present the architecture design requirements to perform

HGNNs with high performance. First, to improve the utilization of various hardware components, a novel stage-fusion methodology is required to fuse stages that exhibit different execution bounds. We propose a stage-fusion programming model along with a customized hardware datapath to enable seamless pipelined execution without any stalls. Second, the high-degree inter-semantic-graph parallelism and data reusability can be exploited to improve performance and efficiency. It is necessary to design specific computing, memory access, and control units to exploit them. Meanwhile, workload-aware scheduling is proposed to ensure workload balance among pipelines without increasing the latency, and similarity-aware execution scheduling is employed to remove the redundancy compute.

### 4 ARCHITECTURE DESIGN

This section presents HiHGNN, a high-performance HGNN accelerator designed to exploit both the high-degree intra- and intersemantic-graph parallelism and data reusability. We begin by introducing a stage-fusion programming model and a novel hardware datapath coordinating with it in Section 4.1 that effectively enables the fusion and pipeline of stages with different execution bounds. Next, we design an independency-aware parallel execution for the inter-semantic-parallelism exploitation, which involves the scale-up and workload balancing optimizations in Section 4.2. Finally, we propose a similarity-aware execution scheduling to maximize the reuse of intermediate results across the processing of semantic graphs in Section 4.3.

# 4.1 Bound-aware Stage Fusion

As mentioned in Section 3.1, different stages of HGNN exhibit diverse execution bounds, leading to unbalanced utilization across different hardware components and limited performance. Although previous efforts [27], [66], [74], [77] have employed stage-fusion techniques to achieve better parallelism in traditional workloads, they lack awareness of execution bounds and fail to match the workflow of HGNNs. This inspires us to propose a bound-aware stage fusion methodology for HGNN acceleration, efficiently improving hardware utilization and exploiting interstage parallelism.

### 4.1.1 Stage-fusion Programming Model

To fully utilize hardware resources and implement pipeline execution, we propose a novel programming model in which the original execution stages are decomposed and reorganized, allowing the fusion and pipeline of execution for stages with different execution bounds. This model is illustrated in Algorithm 2. Note that all the functions included are user-definable, maintaining good programming flexibility and adaptability for various HGNN models. All stages except for the final stage can be executed in parallel as long as their corresponding task lists are non-empty. Overall, this differs significantly from the sequential execution of stages shown in Algorithm 1.

We have made the following modifications and optimizations compared to the original programming model. ① To achieve stage fusion, we break the barrier that separates the NA stage from the FP stage in the original programming model. The original NA stage is split into two steps, i.e., the computation of attention coefficients (lines 8) and the rest of the process (line 12). Then we integrate the former step with the FP stage, enabling directly forwarding the projected features for the computation of attention

# **Algorithm 2: Stage-fusion Programming Model**

```

1 Input: semantic graphs of G = \{G^{\mathcal{P}_1}, G^{\mathcal{P}_2} \dots G^{\mathcal{P}_n}\};

2 Output: the embedding h_v of each vertex v;

3 Initial: all task lists are empty.

for semantic graph G^{\mathscr{P}} \in G do

NA task list=E^{\mathcal{P}};

FP Stage

for each vertex v in FP_task_list do

h_{\nu}'=Feature_Projection(W^{c_{\nu}}, h_{\nu});

\theta_{v}^{\mathscr{P}}=Compute_Coefficient(a_{\mathscr{P}}^{T}, h_{v}');

8

⊲ NA Stage

for each edge e_{u,v} in NA_\overline{task\_list} do

10

11

if x_v and x_u is projected then

z_v^{\mathscr{P}} \leftarrow \text{Aggregate}(\theta_u^{\mathscr{P}}, \theta_v^{\mathscr{P}}, h_u');

12

if all neighbors of v have finished NA then

13

Send_to_LSF_task_list(v);

14

15

16

else

Send_to_FP_task_list(u,v);

17

end

18

end

19

for each vertex v in LSF_task_list do

w_{\mathscr{D}} \leftarrow \text{Compute\_and\_Accumulate}(q^T, z_{v}^{\mathscr{D}});

21

if all vertex in G^{\mathcal{P}} have finished LSF then

22

23

Send_to_GSF_task_list(w_{\mathcal{P}});

end

24

25

end

□ Global SF Stage

for each w@ in GSF_task_list do

26

27

\beta_G \leftarrow \text{Compute\_and\_Accumulate}(w_{\mathscr{D}});

for vertex \ v \in V^{\mathscr{P}} do

28

z_{\nu} \leftarrow \text{Aggregate}(w_{\mathscr{D}}, z_{\nu}^{\mathscr{D}})

29

30

end

31

end

32 end

Final Stage

33 for vertex \ v \in V do

h_{\nu}\leftarrow \text{EW-DIV}(z_{\nu},\beta_G);

35 end

```

coefficients without waiting for all vertex features to be projected. 2 We remove the barrier between the NA and SF stages in most HGNNs. The barrier exists because the HGNNs require all results from different semantic graphs to generate the semantic attention importance in the NA stage. So, we decompose the SF stage into two stages, namely the Local SF (LSF) stage and the Global SF (GSF) stage. For a given semantic graph  $G^{\mathcal{P}}$ , the former mainly involves the intermediate computation of the semantic attention importance (line 21), which is executed once after all the neighbors of a target vertex in  $G^{\mathcal{P}}$  are aggregated. While the latter generates the ultimate semantic attention importance of  $G^{\mathcal{P}}$ (line 27) and performs the semantic aggregation of all the target vertices (lines 28-30). It is executed once for each semantic graph when all the target vertices have accomplished their neighbor aggregation processes. In this way, the LSF stage can be fused into the execution of the NA stage (lines 13-15).

Noticed that in the stage-fusion programming model, we implement the fine-grained parallelism between the FP stage and the NA stage. At this point, if the FP stage is still being used for driving like in the original programming model, then every time a vertex is projected in the FP stage, the NA stage has to search for its neighbors in the edge list or adjacency matrix, which triggers a large number of random accesses and degrades the performance. To reduce the random accesses, we put all edges in the NA\_task\_list, which eliminates the random access for neighbor search. In this way, although the access to the feature becomes

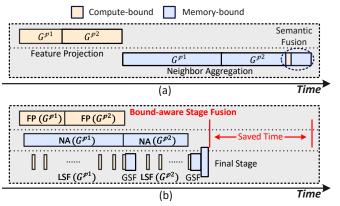

Fig. 4. Execution flow of HGNN programming model: (a) Traditional staged programming model; (b) Bound-aware stage-fusion programming model.

random, the feature itself has a larger dimension, thus the impact on overall bandwidth utilization is relatively small.

Fig. 4 illustrates the difference in the execution flow between the traditional one (Fig. 4 (a)) and our programming model (Fig. 4 (b)). By decomposing and fusing the execution flow, we can combine the execution of the compute-bound FP stage and the memory-bound NA stage. Besides, we can also fuse the compute-bound LSF stage with its preceding memory-bound NA stage to improve the utilization of compute and bandwidth resources simultaneously. Additionally, we pipeline the execution of each stage, enabling the different stages to run in parallel, thus resulting in performance improvement.

### 4.1.2 Implementation of Hardware Datapath

In conjunction with the proposed programming model, we implement several hardware components to constitute to hardware datapath in microarchitecture. We employ a hybrid architecture to minimize the design complexity of hardware components, as in work [7], [25], [66], [73]. This enables us to facilitate data path optimization and leverage parallelism as well as data reusability more effectively.

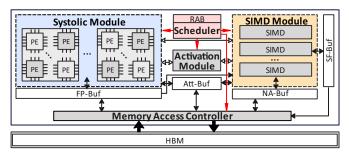

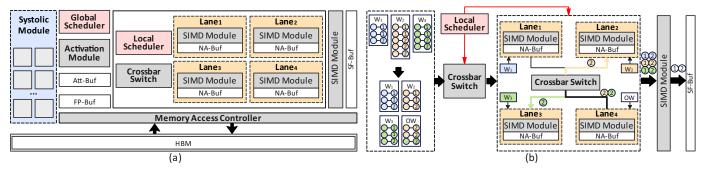

Hardware Components. Throughout the execution of the HGNN models, computational workloads are mainly occupied by matrix-vector multiplication (MVM) and element-wise (EW) operations. To boost their execution efficiency, we design a dedicated module for each of them as depicted in Fig. 5. First, a flexible *Systolic Module* is established for the MVM operations, which is based on the well-known systolic array design [25]. Two execution modes, one for fine-grained matrix multiplication and the other for larger-scale matrix operation, are employed as suggested in work [66]. Second, EW operations running through the whole processing of HGNNs are performed by the *SIMD Module*. In addition, the *Activation Module* is built to perform nonlinear functions like *LeakyRelu*, *Elu*, and *Softmax*. To coordinate

Fig. 5. Basic design of HiHGNN architecture.

workloads across various hardware components, we introduce a centralized *Scheduler* equipped with a redundancy-aware bitmap (RAB) which is built by a set of two-port SRAM banks to support the reuse of intermediate results. The RAB will be further explained in Section 4.3.1.

The high-bandwidth memory (HBM) stores information about the original semantic graphs, mainly including the adjacent information in the compressed sparse column (CSC) format and raw features stored continuously according to vertex categories. Feature Projection Buffer (FP-Buf) and Neighbor Aggregation Buffer (NA-Buf) aim to cache the projected features and the intermediate neighbor aggregated features respectively for data reuse. Similar to NA-Buf, Semantic Fusion Buffer (SF-Buf) is used to hold the features that are aggregated from multiple semantic graphs for vertices. During the computation process of the attention mechanism, a series of parameters as well as intermediate results, are cached in the Attention Buffer (Att-Buf). The Memory Access Controller is used to schedule the data interactions between the on-chip buffers and HBM.

**Hardware Datapath.** The hardware datapath of our proposed stage-fusion programming model is built from the fundamental hardware components we stated above and represents the dataflow during execution.

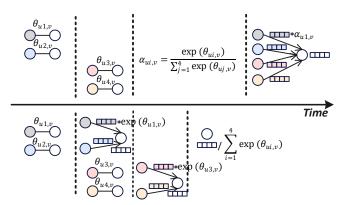

The main challenge in building the hardware datapath is to remove the pipeline stall. On one hand, the data access conflicts caused by fine-grained parallelism with edge-centric granularity increase the access latency, and on the other hand, the accumulation of *Softmax* functions on the denominator also leads to pipeline stalls. For the former we can utilize multi-port SRAM to realize on-chip buffers, while for the latter we need to further decompose the execution flow of *Softmax*. Take the weighted aggregation of NA stage as an example, the decomposition is as follows:

$$\sum_{u \in \mathcal{N}_{v}^{\mathscr{P}}} \alpha_{u,v}^{\mathscr{P}} \cdot h_{u}^{'} = \frac{\sum_{u \in \mathcal{N}_{v}^{\mathscr{P}}} exp(\theta_{u,v}^{\mathscr{P}}) \cdot h_{u}^{'}}{\sum_{k \in \mathcal{N}_{v}^{\mathscr{P}}} exp(\theta_{k,v}^{\mathscr{P}})}$$

The weighted aggregation in the GSF stage also employs a similar approach. An example is illustrated in Fig. 6. Once the numerator is computed, it can be immediately used for aggregation and accumulated onto the denominator, avoiding pipeline stalls caused by waiting for the computation of *Softmax* denominator.

Fig. 6. Optimized execution flow of Softmax function.

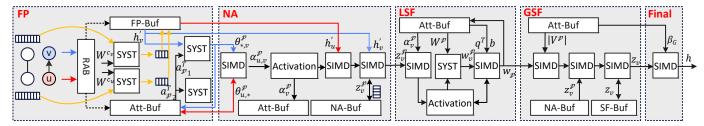

The resulting datapath is depicted in Fig. 7. For each edge  $e_{u,v}$ , the raw features of the source vertex u and the target vertex

Fig. 7. Hardware datapath for the stage-fusion programming model.

$\nu$  are projected into the same vector space through a linear transformation function performed by the *Systolic Module* (indicated by SYST in Fig. 7). A bitmap-based data reuse mechanism is employed here to remove computation redundancy. Since  $h'_u$  and  $h'_{\nu}$  are globally reusable while  $\theta_{u,*}^{\mathcal{P}}$  and  $\theta_{*,\nu}^{\mathcal{P}}$  ( $\theta_{u,*}^{\mathcal{P}}$  for source vertex and  $\theta_{*,\nu}^{\mathcal{P}}$  for target vertex) are only reusable within the same semantic graph, a total of three cases arise for the reuse mechanism, as indicated by the different colored lines in Fig. 7. More details are given in Section 4.3.1.

Unlike the traditional HGNN execution process, after obtaining  $h'_u$  and  $h'_v$ , instead of writing them back and keeping them until aggregation in the NA stage, they are immediately sent to the *Systolic Module* for the computation of  $\theta^{\mathscr{P}}_{u,*}$  and  $\theta^{\mathscr{P}}_{*,v}$  in NA stage, and the weighted aggregation operation from u to v is completed by the *SIMD Module* afterward.

For each target vertex v in  $G^{\mathcal{P}}$ , once all the features of neighbors have been aggregated by the *SIMD Module*, a partial computation of the semantic importance  $w_{\mathcal{P}}$  contributed by v denoted as  $w_v^{\mathcal{P}}$  is carried out using the *Systolic Module* instantly. Meanwhile, the value is accumulated in the ultimate result of  $w_{\mathcal{P}}$ . When all vertices in  $G^{\mathcal{P}}$  finish the FP, NA, and LSF stages, the GSF stage first computes the ultimate semantic importance  $w_{\mathcal{P}}$  of  $G^{\mathcal{P}}$  by dividing it with the total number of vertices  $V^{\mathcal{P}}$  and then aggregates the semantic features of all vertices in  $G^{\mathcal{P}}$ , which is similar to NA and is performed on *SIMD Module*. Following the completion of all the aforementioned stages, the final embeddings h are produced by dividing target vertices' features by an accumulated global weight  $\beta_G$ .

# 4.2 Parallelism Exploitation: Independency-aware Parallel Execution

In this section, we propose the independency-aware parallel execution to exploit the inter-semantic-graph parallelism by leveraging the independency among semantic graphs.

### 4.2.1 Scale-up Optimization for Basic Architecture

To dig into the parallelism across semantic graphs, we provide the scale-up optimization for the above architecture.

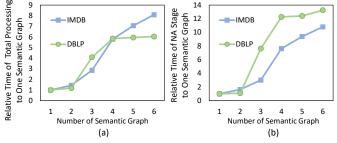

Fig. 8. Relative time of execution to one semantic graph: (a) Time of total execution; (b) Time of NA stage.

We first give the motivation to exploit inter-semantic-graph parallelism. First, the processing of each semantic graph in the NA stage is independent. Second, the NA stage dominates the total execution time of HGNNs, as demonstrated in Section 3. Third, the execution time of total execution and the NA stage both increase as the number of semantic graphs increases, as demonstrated in Fig. 8 (a) and (b). Therefore, it is vital to exploit the parallelism across semantic graphs.

To this end, a scale-up optimization for the basic architecture as shown in Fig. 9 (a) is presented. The basis for scaling up is the extension of the lanes and each lane independently processes a semantic graph. For simplicity, we refer to the basic design of HiHGNN as a single-lane architecture, while the scale-up design of HiHGNN is called a multi-lane architecture. In the multi-lane architecture, the hardware components are generally the same as those in the single-lane one. The Systolic Module is mainly responsible for MVM operations, while the SIMD Module handles EW operations. To schedule the execution, we replace the original Scheduler with Global Scheduler which schedules the lane group with other modules. A scheduler named Local Scheduler is used to handle the processing within the lane group. An additional SIMD Module outside to execute the GSF stage after synchronizing the results of different lanes. Besides, to allocate the workload to each lane and achieve dynamic scheduling across them, we leverage crossbar switches with the number of ports being consistent with the number of lanes for data transmission, which is illustrated in detail in the next section.

# 4.2.2 Workload Balance across Hardware Datapaths

To make full use of compute units, we propose workload-aware scheduling to balance the workload across different lanes.

With the scale-up design, the multi-lane architecture can leverage both stage-level parallelism and semantic-graph-level parallelism. However, the workload imbalance across different semantic graphs is severe in real-world datasets. For example, the DBLP dataset consists of three semantic graphs, each containing 4057 vertices, but with vastly different numbers of edges, i.e., 7043571, 5000496, and 11113, respectively. When the three workloads are assigned directly to the *Lane*<sub>1</sub>, *Lane*<sub>2</sub>, and *Lane*<sub>3</sub>. *Lane*<sub>1</sub> and *Lane*<sub>2</sub> become overloaded, while *Lane*<sub>3</sub> is underloaded.

Additionally, to avoid introducing extra overhead during the execution process, we require a low-latency and stable algorithm to balance the workloads. Fortunately, unlike the situation in the previous work [6], there are no computational dependencies between different workloads. This advantageous characteristic allows us to adopt a low-cost strategy to achieve workload balance among lanes.

To fully utilize the compute resources, we propose workloadaware scheduling illustrated in Fig. 9 (b) on a four-lane architecture. We denote the initial workloads received by the global scheduler from three semantic graphs during a specific period as

Fig. 9. Independency-aware parallel execution: (a) Scale-up optimization for basic architecture; (b) Workload balance by workload-aware scheduling.

$W_1$ ,  $W_2$ ,  $W_3$ , respectively, and the four lanes as  $Lane_1$ ,  $Lane_2$ ,  $Lane_3$  and  $Lane_4$ . The allocation threshold for each lane is set to the maximum number of edges that the lane can process once. In this example, the threshold is set to three. During the runtime, the Local Scheduler first identifies each task list that exceeds the threshold and pushes the excess parts into a task list Overflow Workload (OW) to prevent any blocking in the execution. Once none of the task lists exceeds the threshold, the Local Scheduler assigns the task lists to their corresponding lanes, such as  $W_1$  to  $Lane_1$ , except for the OW. Finally, the Local Scheduler assigns the workloads in the OW to the lanes that have not reached the threshold. This scheduling approach ensures that there is no blocking in each lane and maximizes the utilization of the compute units.

For synchronization of intermediate results, the *Local Scheduler* records the aggregation status of each vertex. When a vertex finishes NA, all lanes that have the partial aggregation results of this vertex send these results to the lane it is originally assigned to in the workloads dispatch. As an example, in this case, the vertices executed on  $L_4$  are transferred to  $L_2$  and  $L_3$  for the LSF stage. When all vertices within a semantic graph have been finished the LSF stage, the results are sent to an outside *SIMD Module* for the GSF stage and then stored in SF-Buf.

# 4.3 Data Reusability Exploitation: Similarity-aware Execution Scheduling

Due to the fine-grained execution flow, it inevitably introduces a significant amount of redundant computations and DRAM accesses. To address this issue and eliminate redundant computations and DRAM accesses within and across the processing of semantic graphs, we initially employ a basic data-reuse technique. Building on this foundation, we further propose a similarity-aware execution scheduling to exploit the inter-semantic-graph data reusability.

### 4.3.1 Basic Mechanism of Data Reuse

To harvest the reusability of intermediate results both within and across semantic graphs, we implement a basic mechanism for data reuse using a bitmap.

We first give two findings to show the data-reuse opportunity. i) For the prevalent HGNN models, the projected features can be reused within and across semantic graphs in FP stage due to the vertex-type-specific projection. ii) As illustrated in Algorithm 2, the attention importance used for the aggregation from the source vertex u to the target vertex v in the NA stage can be generated from  $\theta_{u,*}^{\mathscr{P}}$  and  $\theta_{*,v}^{\mathscr{P}}$ , which are derived from  $h_u'$  and  $h_v'$  directly. These coefficients can be reused for all edges, avoiding recomputations for each edge.

TABLE 4

The status of feature vector encoded by RAB.

| _    | Status    |                                         |                                         |  |

|------|-----------|-----------------------------------------|-----------------------------------------|--|

|      | Projected | Calculated $\theta_{u,*}^{\mathscr{S}}$ | Calculated $\theta_{*,v}^{\mathscr{S}}$ |  |

|      | 0         | 0                                       | 0                                       |  |

| Code | 1         | 0                                       | 0                                       |  |

|      | 1         | 1                                       | 0                                       |  |

|      | 1         | 0                                       | 1                                       |  |

|      | 1         | 1                                       | 1                                       |  |

Based on these findings, we implement a bitmap called RAB to keep track of whether the computation for a given vertex has been performed or not. We record both the projected features and the attention coefficients to eliminate redundant computation within and across semantic graphs. However, since each vertex in every semantic graph has multiple status, providing separate bitmaps for each individual case will significantly increase overhead. Thus, we integrate the RAB into the Local Scheduler and employ the binary encoding approach to assign three bits to each vertex, which are used to record its status. These bits are indexed by the pair (type, index). The encoding of the bitmap is shown in Table 4. Before starting the feature projection for a vertex v, the Global Scheduler first checks the bitmap for its corresponding bits. If it is filled with full zeros, the vertex's current feature vector needs to be projected. Similarly, the middle and lowest bits indicate whether the attention coefficients in that semantic graph corresponding to the vertex have been generated.

Meanwhile, a raw feature is solely accessed from DRAM for the first projection of a vertex in scenarios where RAB is utilized. Subsequently, the projected features and attention coefficients can be directly read from either DRAM or on-chip buffer for subsequent computations, thereby eliminating the need for repetitive access to raw features in DRAM.

### 4.3.2 Similarity-aware Execution Scheduling

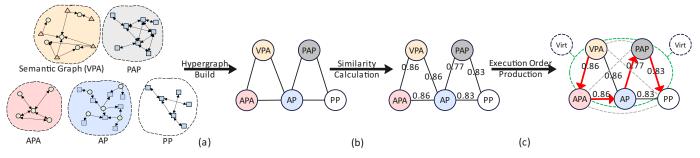

To further exploit the data reusability across semantic graphs, we propose a similarity-aware execution scheduling by adjusting the execution order of semantic graphs based on the similarity between semantic graphs. All the scheduling occurs in the preprocessing, which can be included in the SGB stage.

For the prevalent HGNN models, each type of vertex is projected only once across all semantic graphs, and stored in the FP-Buf for reuse. Therefore, if there is a significant overlap (similarity) in vertex types between two consecutive semantic graphs, the latter semantic graph can reuse the projected feature left in the FP-Buf by the former semantic graph. This can help avoid duplicate DRAM accesses and improve performance. For instance, considering that the heterogeneous graph includes semantic graphs {AP, PT, PP, APA, AVA}, one of the best scheduling orders is APA-AVA-AP-PP-PT. In this way, the semantic graph APA loads

Fig. 10. Similarity-aware execution scheduling: (a) Hypergraph build; (b) Similarity calculation; (c) Execution orders production by shortest Hamilton path algorithm.

the feature of vertex A, which can be left in the FP buffer and reused by the subsequent semantic graphs such as AVA and AP; after the semantic graph AP is executed, the feature of vertex P replaces the feature of vertex A in the FP buffer and can be reused by the following semantic graphs PP and PT.

To identify the reusability of data between semantic graphs, we represent each semantic graph as a vertex in a hypergraph, as shown in Fig. 10 (a). In the hypergraph, each edge connects two semantic graphs that have at least one common type of vertex. This means that the projected features of the common vertices can be reused, promoting computational efficiency. To measure the similarity between two connected semantic graphs, we assign a weight to the edge that reflects their similarity as shown in Fig. 10 (b). The weight is calculated using the following formula:  $w_e = 1 - \eta_e / \sum_{i \in E} \eta_i$ , where E is the set of all edges in the hypergraph and  $\eta_e$  is the number of common vertices in the two semantic graphs connected by the edge e. A lower weight value of  $w_e$  indicates a higher similarity between the two semantic graphs, implying that more projected features can be reused.

After the hypergraph is built, the scheduling of the execution order of semantic graphs is transformed to finding a path that starts from a specific semantic graph and passes through all other semantic graphs exactly once. The objective is to maximize the similarity across all sequentially executed semantic graphs, thereby achieving more reuse of intermediate results. To accomplish this, we utilize the *Shortest Hamilton Path* algorithm on the hypergraph to determine a specific order sequence of semantic graphs for execution.

There are still two challenges need to be addressed. First, not all hypergraphs created by semantic graphs are *Hamiltonian graphs*, which means that *Hamilton paths* are not always found. Second, since there is no inherent execution priority among semantic graphs, the beginning and ending points of the *Hamilton path* are random. Therefore, as shown in Fig. 10 (c), we first add extra edges to the hypergraph with a weight of 1, represented by gray dashed connections, which makes hypergraph a complete graph. Second, we add two virtual vertices to the hypergraph, which are connected to all other vertices with weights of zero, represented by the green dashed connections with virtual vertices. These virtual vertices are then used as the beginning and ending points of the *Hamilton path*, respectively. Finally, the execution orders of semantic graphs are produced by the shortest Hamilton path algorithm.

### 5 Experimental Methodology

**Methodology.** The performance and energy of HiHGNN are evaluated using the following tools.

TABLE 5 Information of HetG datasets.

| Dataset | #Vertex                                                                       | #Feature                              | #Edge of Each Relation                                                                | Metapath                   |

|---------|-------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------|----------------------------|

| IMDB    | movie (M): 4932<br>director (D): 2393<br>actor (A): 6124<br>keyword (K): 7971 | M: 3489<br>D: 3341<br>A: 3341<br>K: — | AM: 14779 MA: 14779<br>KM: 23610 MK: 23610<br>DM: 4932 MD: 4932                       | MDM<br>MAM<br>MKM          |

| ACM     | paper (P): 3025<br>author (A): 5959<br>subject (S): 56<br>term (T): 1902      | P: 1902<br>A: 1902<br>S: 1902<br>T: — | TP: 255619 PT: 255619<br>SP: 3025 PS: 3025<br>PP: 5343 -PP: 5343<br>AP: 9949 PA: 9949 | PPSP<br>PSP<br>PPAP<br>PAP |

| DBLP    | author (A): 4057<br>paper (P): 14328<br>term (T): 7723<br>venue (V): 20       | A: 334<br>P: 4231<br>T: 50<br>V: —    | AP: 19645 PA: 19645<br>VP: 14328 PV: 14328<br>TP: 85810 PT: 85810                     | APA<br>APTPA<br>APCPA      |

Cycle-accurate Simulator. For the performance evaluation, a customized cycle-accurate simulator is designed and implemented to measure execution time in the number of cycles. This simulator models the microarchitectural behavior of each hardware module of HiHGNN. In addition, a detailed cycle-accurate on-chip memory model is implemented and integrated. This is also integrated with Ramulator [26], a cycle-accurate DRAM simulator, to simulate the cycle-accurate behavior of DRAM accesses to HBM.

CAD Tools. For area, power, and critical path delay measurements, we implement an RTL version of each hardware module and synthesize it. We use the Synopsys Design Compiler with the TSMC 12 nm standard VT library for the synthesis and estimate the power consumption using Synopsys PrimeTime PX. The slowest module has a critical path delay of 0.83 ns including setup and hold time, putting HiHGNN comfortably at the 1 GHz clock frequency.

Memory Measurements. The access latency, energy, and area of the on-chip buffers are estimated using Cacti 6.5 [1]. We use four different scaling factors to convert them to 12 nm technology, as depicted in work [44], [57] since Cacti only supports down to 32 nm technology. The access latency and energy of HBM1.0 are simulated by Ramulator and estimated with 7 pJ/bit as in the work [45], respectively.

Benchmark Datasets and HGNN Models. The benchmark datasets that we used are listed in Table 5. The raw features of each vertex are provided by the dataset itself. The scale of heterogeneous graph datasets differs from that of homogeneous graph datasets in terms of calculation methods. The size of homogeneous graph datasets is determined by the number of edges and vertices they exhibit, while the size of heterogeneous graph datasets is determined by the construction of semantic

TABLE 6

Platforms for HiHGNN and baselines.

|             | Т4                | A100            | HiHGNN (4 Lanes)   |

|-------------|-------------------|-----------------|--------------------|

| Peak        | 8.1 TFLOPS,       | 19.5 TFLOPS,    | 16.38 TOPS,        |

| Performance | 1.59 GHz          | 1.41 GHz        | 1.0 GHz            |

|             |                   |                 | 2.44 MB (FP-Buf),  |

| On-chip     | L1 Cache 1.28 MB, | L1 Cache 20 MB, | 14.52 MB (NA-Buf), |

| Buffer      | L2 Cache 4 MB     | L2 Cache 40 MB  | 0.12 MB (SA-Buf),  |

|             |                   |                 | 0.38 MB (Att-Buf)  |

| Off-chip    | 300 GB/s,         | 1935 GB/s,      | 512 GB/s,          |

| Memory      | GDDR6             | HBM2e           | HBM1.0             |

Note: The compute units include 96 systolic arrays (each with 8×8 MACs) and 128 8-way SIMD cores for each lane.

graphs by the metapaths. For instance, in the experiment, the three datasets include 92,760, 82,384, and 133,910 vertices, and 630,542, 6,309,372, and 24,669,366 edges, respectively. Four popular HGNN models are used, including HAN [62], R-GCN [47], R-GAT [58], and S-HGN [40], which are widely adopted in the evaluation of algorithm community [17], [40], [70].

Baseline Platforms. To compare the performance of HiHGNN to the state-of-the-art work, all HGNN models are implemented using a state-of-the-art framework DGL 1.0.2 [59] and evaluated on an NVIDIA GPU T4 and an NVIDIA GPU A100, using the NVIDIA Nsight Compute. All models are implemented with the same number of hidden units {64} and layers are {1, 3, 3, 2} for {HAN, R-GAT, R-GCN, S-HGN}, respectively. In addition, we implement the above HGNN models in HiHGNN. All models are implemented with the same number of hidden units and layers used in GPUs. Table 6 lists the configurations for the above implementations.

It should be noted that utilizing our proposed optimizations in GPU platform may result in the loss of hardware-optimized benefits on GPUs, which could outweigh the potential gains. This is because: i) GPUs accelerate HGNNs using coarse-grained hardware-optimized operations (i.e., SpMM) which are sophisticatedly optimized in hardware level; ii) Our optimizations are based on decoupling coarse-grained operations into finer-grained ones.

### 6 EXPERIMENTAL RESULTS

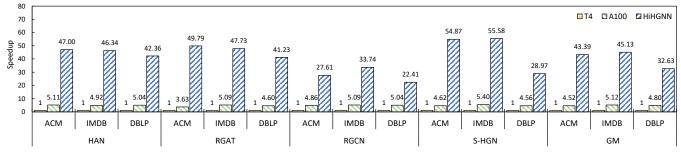

In this section, we compare HiHGNN with the baselines and present the optimization analysis in detail. The last set of bars in the figures, labeled GM, shows the geometric mean across all HGNN models.

### 6.1 Overall Results

**Speedup.** Fig. 11 shows the speedup of HiHGNN to GPU T4. Hi-HGNN achieves an average speedup of 40.0× and 8.3× compared to GPU T4 and A100, respectively. The performance improvement of HiHGNN is attributed to the well-designed hardware datapath for HGNN and the efficient exploitation of inter-semantic-graph parallelism and data reusability. First, the bound-aware stage-fusion programming model and its corresponding hardware datapath help greatly improve compute utilization and bandwidth utilization across all stages. Second, an independency-aware parallelism exploitation optimization helps leverage more hardware resources to improve performance. Third, the similarity-aware execution scheduling significantly reduces the random accesses

TABLE 7

Characteristics of HiHGNN (TSMC 12 nm).

| Area (mm <sup>2</sup> )       | %                                                                               | Power (mW)                                                                                                                                         | %                                                                                                                                                                                                                                |  |  |

|-------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 21.36                         | 100                                                                             | 12001.87                                                                                                                                           | 100                                                                                                                                                                                                                              |  |  |

| Breakdown by Functional Block |                                                                                 |                                                                                                                                                    |                                                                                                                                                                                                                                  |  |  |

| 1.80                          | 8.42                                                                            | 202.90                                                                                                                                             | 1.69                                                                                                                                                                                                                             |  |  |

| 10.70                         | 50.11                                                                           | 1207.42                                                                                                                                            | 10.06                                                                                                                                                                                                                            |  |  |

| 0.09                          | 0.41                                                                            | 9.98                                                                                                                                               | 0.08                                                                                                                                                                                                                             |  |  |

| 0.28                          | 1.31                                                                            | 31.60                                                                                                                                              | 0.26                                                                                                                                                                                                                             |  |  |

| 5.10                          | 23.88                                                                           | 6758.40                                                                                                                                            | 56.31                                                                                                                                                                                                                            |  |  |

| 3.19                          | 14.93                                                                           | 3276.80                                                                                                                                            | 27.30                                                                                                                                                                                                                            |  |  |

| 0.09                          | 0.44                                                                            | 440.82                                                                                                                                             | 3.67                                                                                                                                                                                                                             |  |  |

| 0.11                          | 0.50                                                                            | 73.95                                                                                                                                              | 0.62                                                                                                                                                                                                                             |  |  |

|                               | 21.36<br>akdown by Fun<br>1.80<br>10.70<br>0.09<br>0.28<br>5.10<br>3.19<br>0.09 | 21.36   100<br>akdown by Functional B<br>1.80   8.42<br>10.70   50.11<br>0.09   0.41<br>0.28   1.31<br>5.10   23.88<br>3.19   14.93<br>0.09   0.44 | 21.36   100   12001.87<br>akdown by Functional Block<br>1.80   8.42   202.90<br>10.70   50.11   1207.42<br>0.09   0.41   9.98<br>0.28   1.31   31.60<br>5.10   23.88   6758.40<br>3.19   14.93   3276.80<br>0.09   0.44   440.82 |  |  |

to DRAM, resulting in further performance improvement. The detailed analysis of the effects of these optimizations is presented in Section 6.2.

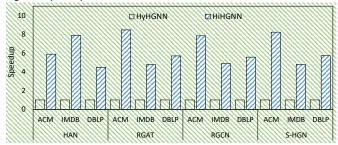

Compare with HyGCN-like Accelerator. As discussed in Section 3.2, existing HyGCN-like accelerators primarily cater to GCN models and lack support for the execution flow of HGNNs. To underscore the advantages of HiHGNN over HyGCN-like accelerators, we modify the execution flow of HiHGNN to align with that of HyGCN-like accelerators, denoting the modified version as HyHGNN. This adaptation involves naïve stage fusion, shifting the parallel granularity from the edge level to the stage level. It is worth noting that the techniques introduced by HiHGNN, such as workload-aware scheduling and similarity-aware execution scheduling, are not incorporated into HyHGNN.

Fig. 12 manifests that the HiHGNN yields a 6.1× improvement over HyHGNN. This improvement primarily stems from the dedicated datapath design tailored for HGNNs. Additionally, HiHGNN's superior parallelism, facilitated by stage-fusion programming and independency-aware parallel execution, contributes to the enhanced performance. Furthermore, the efficient data reuse mechanism of HiHGNN, specifically the similarity-aware execution scheduling, plays a crucial role in driving these performance gains.

**Area and Power.** Table 7 provides a detailed breakdown of the area and power of HiHGNN (except for DRAM), which are 21.36 mm<sup>2</sup> and 12.00 W, respectively. The buffers that include FP-Buf, NA-Buf, SF-Buf, and Att-Buf occupy 60.25% area and consume 12.10% power. SIMD Module and Systolic Module are the main computing units that produce 38.81% and 83.61% power, respectively. For the computation precision, we use a 32-bit integer that is enough to maintain the accuracy of HGNN inference.

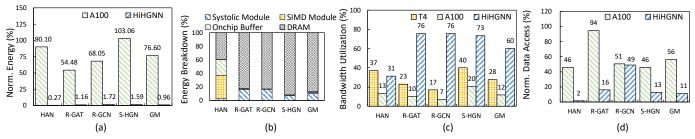

Energy and Its Breakdown. Fig. 13 (a) shows that HiHGNN achieves the average energy reduction with 99.59% and 99.74% compared to GPU T4 and GPU A100, respectively. The energy consumption of all platforms includes the DRAM. There are two factors mainly contributing to the overall reduction in energy consumption. First, the reduction of execution time leads to a decrease in energy consumption. Second, the exploitation of data reusability greatly reduces DRAM accesses, reducing energy consumption as well.

Fig. 13 (b) shows the breakdown of the energy consumption of different HGNNs models. First, the energy consumed by DRAM accesses occupies most of the energy consumption in all models. Second, the HAN model incurs a higher energy cost on its *SIMD Module* and on-chip buffer than other models because the NA stage occupies the most execution time. Third, both the R-GCN and R-GAT models consume a higher energy consumption in *Systolic Module* compared to other models, due to the long execution time of their FP stage. Fourth, the S-HGN model consumes more

Fig. 11. Speedup over GPU T4.

Fig. 12. The advantage brought by Stage-fusion Programming Model over Naïve Stage Fusion.

energy in the DRAM access, due to the requirement to load both raw features and the additional edge embeddings in the NA stage.

**Utilization of DRAM Bandwidth.** Fig. 13 (c) shows the average utilization of the DRAM bandwidth of HiHGNN and others. HiHGNN reaches 2.1× of GPU T4 and 5.0× of GPU A100 in bandwidth utilization, respectively. The bandwidth utilization for GPUs is limited by the random accesses to projected features, attention coefficients, and edge embeddings. However, those intermediate results are elaborately stored on on-chip buffers in HiHGNN, eliminating random DRAM access. It should be noted that, in the case of the HAN model, the intermediate results in the NA stage are mostly stored in NA-Buf, which significantly reduces the DRAM accesses while also reducing bandwidth utilization.

Number of DRAM Accesses. Fig. 13 (d) shows the total data access to the DRAM of HiHGNN and others during runtime, normalized to GPU T4. HiHGNN dramatically reduces DRAM accesses by 89% and 80% compared to GPU T4 and GPU A100 on average, respectively. HiHGNN reduces the need for DRAM access by elaborately reusing intermediate results that are frequently accessed, such as projected features. From the perspective of the model, the HAN model adopts the type-specific FP stage and attention-based NA stage, and is greatly benefited from the reuse of intermediate results. In addition, HAN also takes advantage of the similarity-aware execution scheduling to remove redundant data accesses at the semantic graph level, resulting in a further reduction of DRAM accesses. On the contrary, the relation-specific FP stage of R-GCN dominates the execution, and significant DRAM accesses to raw features are inevitable.

### 6.2 Effects of Proposed Optimizations

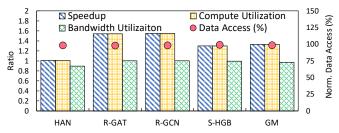

A detailed evaluation on the DBLP dataset is conducted to give more insights into the proposed optimizations. The optimizations include bound-aware stage fusion, independency-aware parallelism exploitation, and similarity-aware execution scheduling. We compare the following combinations to understand the effectiveness of them: 1) w/ and w/o bound-aware stage fusion; 2) the scalability of scale-up architecture as well as w/ and w/o workload-aware scheduling; 3) w/ and w/o similarity-aware execution scheduling.

Effect of Bound-aware Stage Fusion. Fig. 14 depicts the benefit brought by the bound-aware stage fusion. During execution, this technique reduces 35% execution time on average. For the R-GCN and R-GAT models, the time-consuming FP stage greatly benefits from the bound-aware stage fusion, which results in up to 50% improvements in compute utilization and performance. However, for HAN, the NA stage dominates the entire processing time, making the bound-aware stage fusion a limited success.

Effect of Independency-aware Parallel Execution. Fig. 15 illustrates the scalability of HiHGNN and the effect of workload-aware scheduling. Fig. 15 (a) depicts an approximately linear improvement in performance and compute utilization with the increasing number of lanes. This is because the workload-aware scheduling efficiently enables multiple lanes to work together on a single semantic graph, ensuring the scalability of the entire architecture. Fig. 15 (b) gives an ablation study on the impact of workload-aware scheduling. The results demonstrate that this scheduling leads to a gradual improvement in compute utilization and performance with the increasing number of lanes. Noticed, for the HAN model, the total workload consists of three semantic graphs. Therefore, when the number of lanes scales up to four, this scheduling allows for an additional idle lane to be utilized for processing, resulting in a significant improvement.

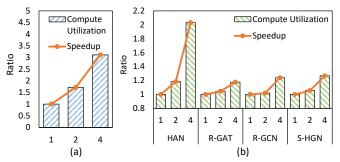

Effect of Similarity-aware Execution Scheduling. Fig. 16 (a) and (b) show the speedup and DRAM data access in the fourlane architecture of HiHGNN with the similarity-aware execution scheduling, respectively, compared to the random scheduling case. Note that the horizontal axis represents the ratio between the size of total projected vertex features and the size of the FP-Buf.

In detail, when the number of semantic graphs is four, the scheduling has limited impact on performance and DRAM data access because of the four-lane architecture. However, as the number of semantic graphs increases to eight and twelve, the scheduling demonstrates better performance improvement and more reduction of DRAM access. This improvement is attributed to the effective reuse of projected features from previous semantic graph by the subsequent one. Furthermore, the prepossessing overhead of this scheduling on CPU is negligible. For instance, on the DBLP dataset, it accounts for less than 0.1% of the end-to-end execution time.

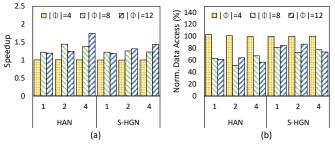

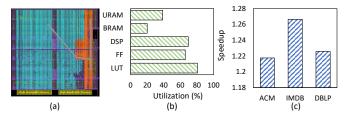

# 6.3 Results on FPGA Implementation

To further validate the feasibility of our design, we implement and evaluate a small single-lane design of HiHGNN on the Xilinx FPGA Alveo U50 accelerator card using Xilinx Vitis Toolchains. Note that due to the limited arithmetic and bandwidth resources on FPGA board, our FPGA prototype implementation is only used to validate the implementability of the architecture and the effectiveness of the strategy.

Fig. 13. Details of results: (a) Normalized energy over GPU T4; (b) Energy breakdown of HiHGNN; (c) DRAM bandwidth utilization of all platforms; (d) Normalized data access to DRAM over GPU T4. We only show results on the DBLP dataset for simplicity.

Fig. 14. Performance comparison of HiHGNN w/ and w/o bound-aware stage fusion.

Fig. 15. Performance comparison of HiHGNN w/ and w/o independency-aware parallel execution: (a) Speedup and compute utilization for a single semantic graph processing in the different number of lanes; (b) Speedup and normalized compute utilization w/ workload-aware scheduling to w/o workload-aware scheduling.

Fig. 16. Performance of HiHGNN w/ and w/o similarity-aware execution scheduling: (a) Speedup and (b) normalized DRAM data access across different ratios and semantic graphs.

Fig. 17. Results on FPGA implementation for a small single lane design: (a) Layout of HiHGNN; (b) Various resources utilization ratios; (c) Speedup of HiHGNN w/ and w/o similarity-aware execution scheduling.

Fig. 17 (a) and (b) respectively present the implementation layout and utilization ratios of various types of resources of FPGA. Fig. 17 (c) shows that HiHGNN achieves an average speedup of

$1.23 \times$  among various datasets with the adoption of the similarity-aware execution scheduling. This result is consistent with the result in the previous subsection.

### 7 RELATED WORK

Due to the outstanding learning capacity of GNNs on graph data, GNN accelerators draw great interest from the architecture community [7], [15], [16], [20], [21], [23], [24], [27], [30], [31], [32], [33], [37], [46], [51], [66], [69], [73].

One part of them [27], [66], [74] employs stage fusion to boost the overall performance. For example, *HyGCN* [66] proposes a hybrid architecture to leverage inter-stage fusion to improve overall performance. *GCoD* [74] proposes a GCN algorithm and accelerator co-design framework dedicated two-pronged accelerator with a separate engine to process each of the denser and sparser workloads. Both of the two engines achieve the inter-stage fusion. *GRIP* [27] decomposes GNN inference into three stages and implements each phase with specialized on-chip memory and execution units, realizing the fusion of these three stages.

The aforementioned accelerators can be categorized as having a design based on parallel pipeline (PP), according to the definition in the literature [14]. In a PP design, the parallel units (i.e., groups of PEs) within the accelerator execute both stages simultaneously. However, the workflow of HGNN involves more intricate execution processes and additional execution stages, resulting in different fusion methodology. Another part of them [7], [33], [46] improves performance by exploiting multi-dimensional parallelism. For example, FlowGNN [46] uses a scalable dataflow architecture to generally support a wide range of GNN models and exploits multiple-level parallelism in terms of the processing of vertices and edges. Unfortunately, previous efforts are ill-suited to exploit the high-degree parallelism and data reusability which are inherent in HGNNs. In addition, most HGNNs leverage attention mechanisms to improve model accuracy. However, most GNN accelerators focus on graph convolutional network (GCN) [28] and GCN variants, failing to perform attention mechanisms. A few other efforts [20], [21], [69] using parameter quantization and model pruning that sacrifice accuracy to accelerate graph attention networks. Their optimizations are orthogonal to ours.